半导体器件的开关特性

门电路

门电路指的是以实现基本逻辑关系和常用复合逻辑关系的电子电路

常用的逻辑门电路:

与门、或门、非门、异或门、与非门、或非门、与或非门

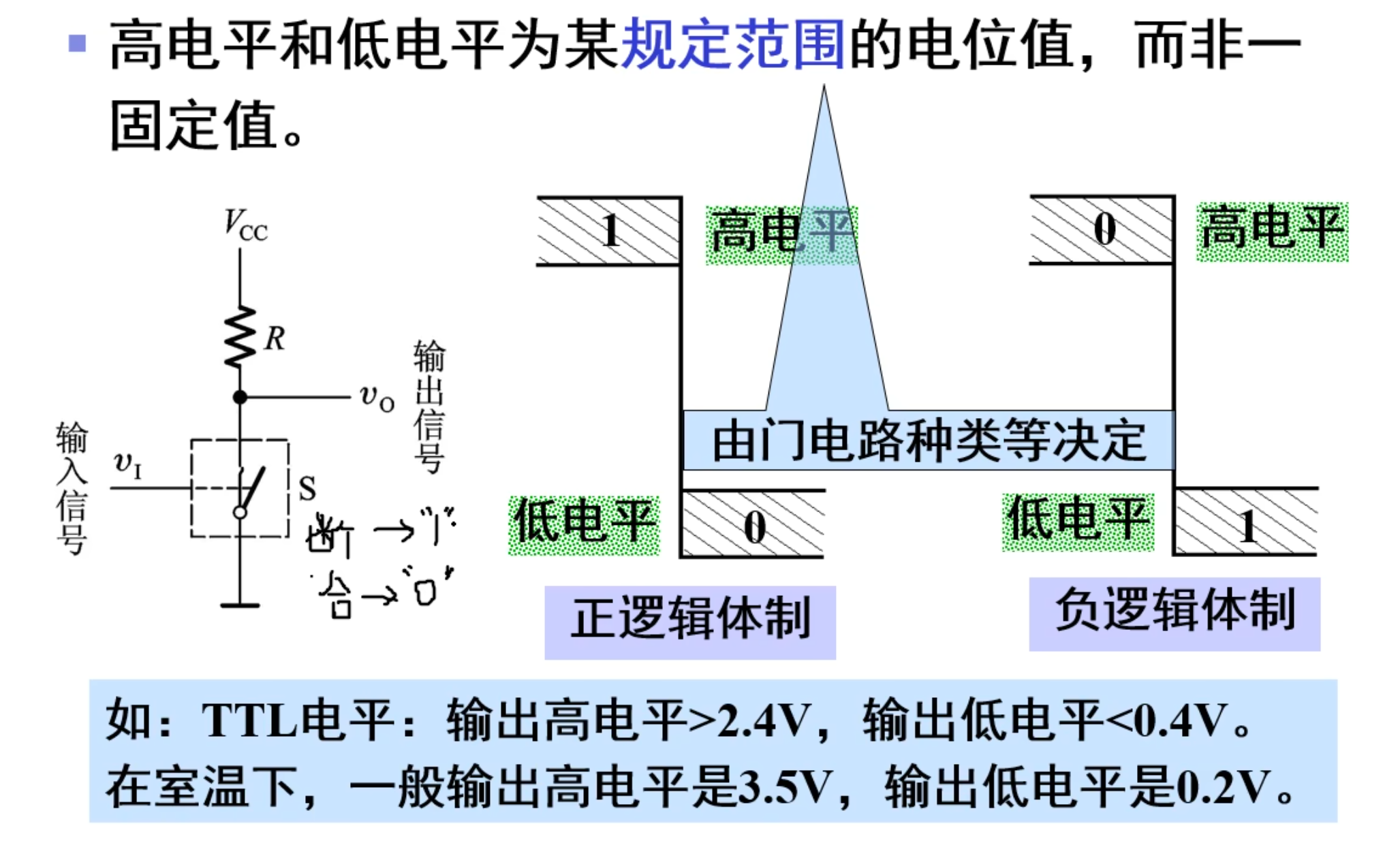

高低电平

高低电平是某一个规定范围内的电位值,而不是一个固定值

二极管的开关特性

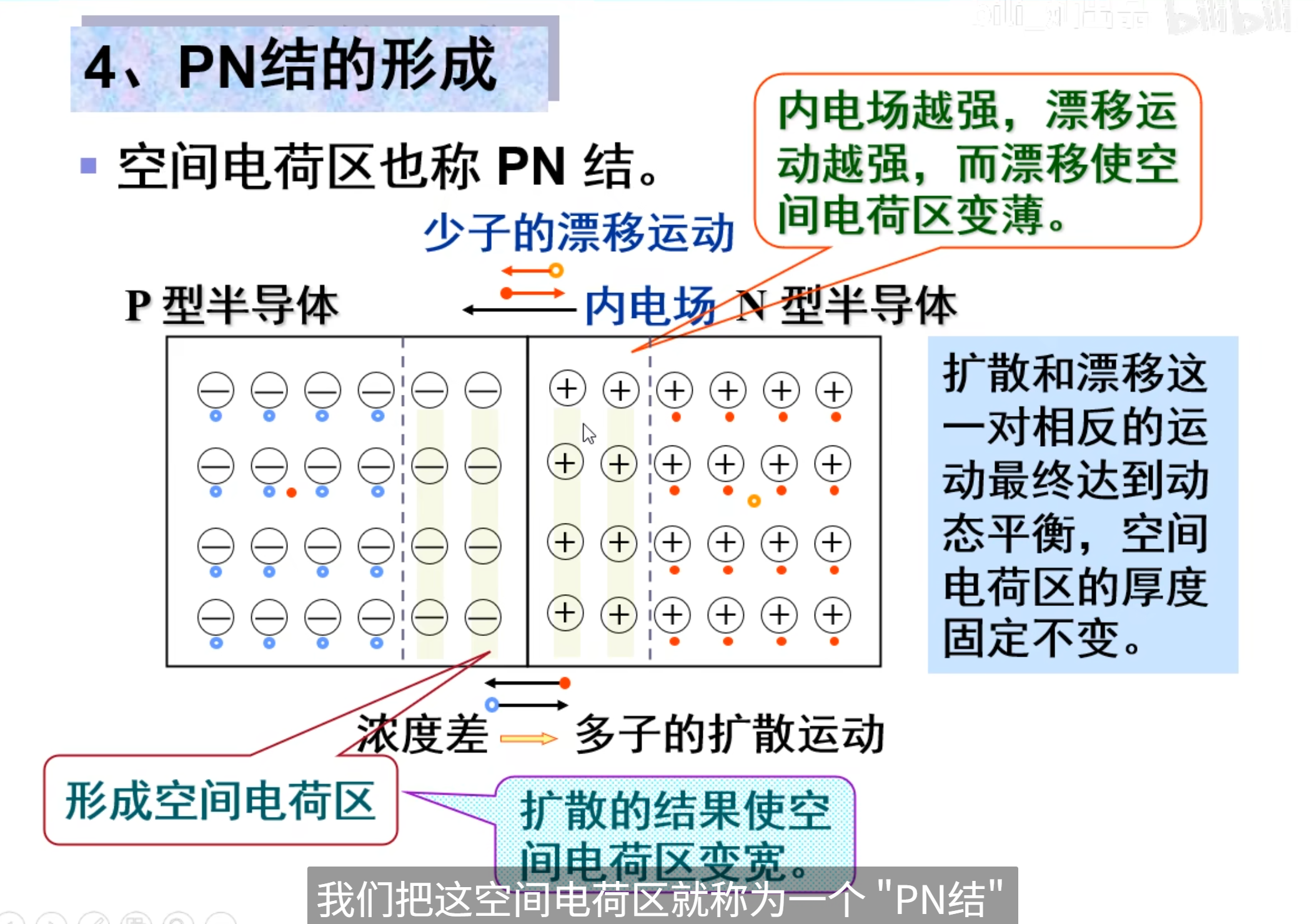

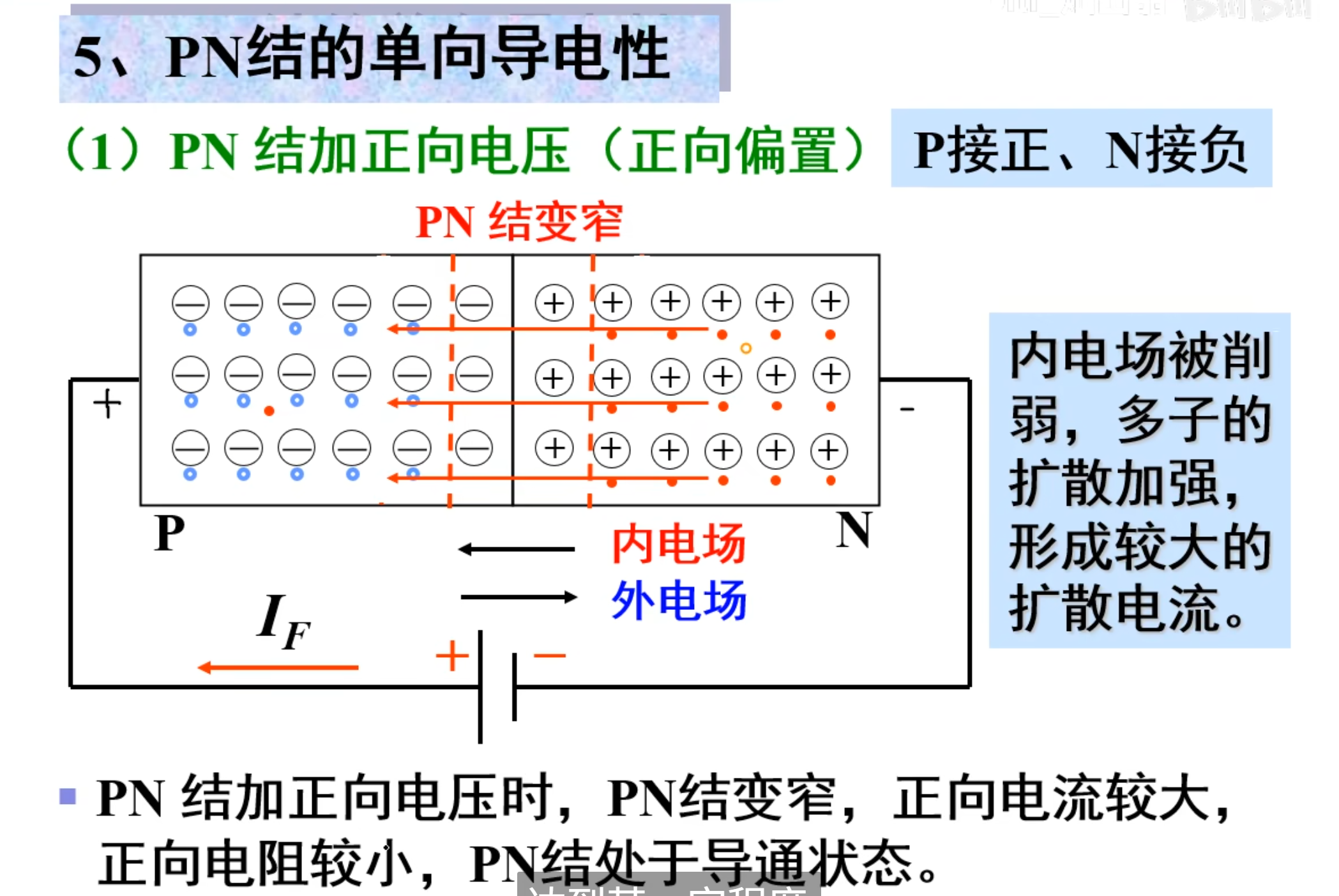

这里只需要直到有两种半导体,一种是 P 半导体,一种是 N 半导体。

三极管

三极管有两种类型,一种是 NPN,一种是 PNP

区分 NPN 形三极管和 PNP 形三极管的关键是看符号上的箭头指向。(箭头一定是指向 N 极)

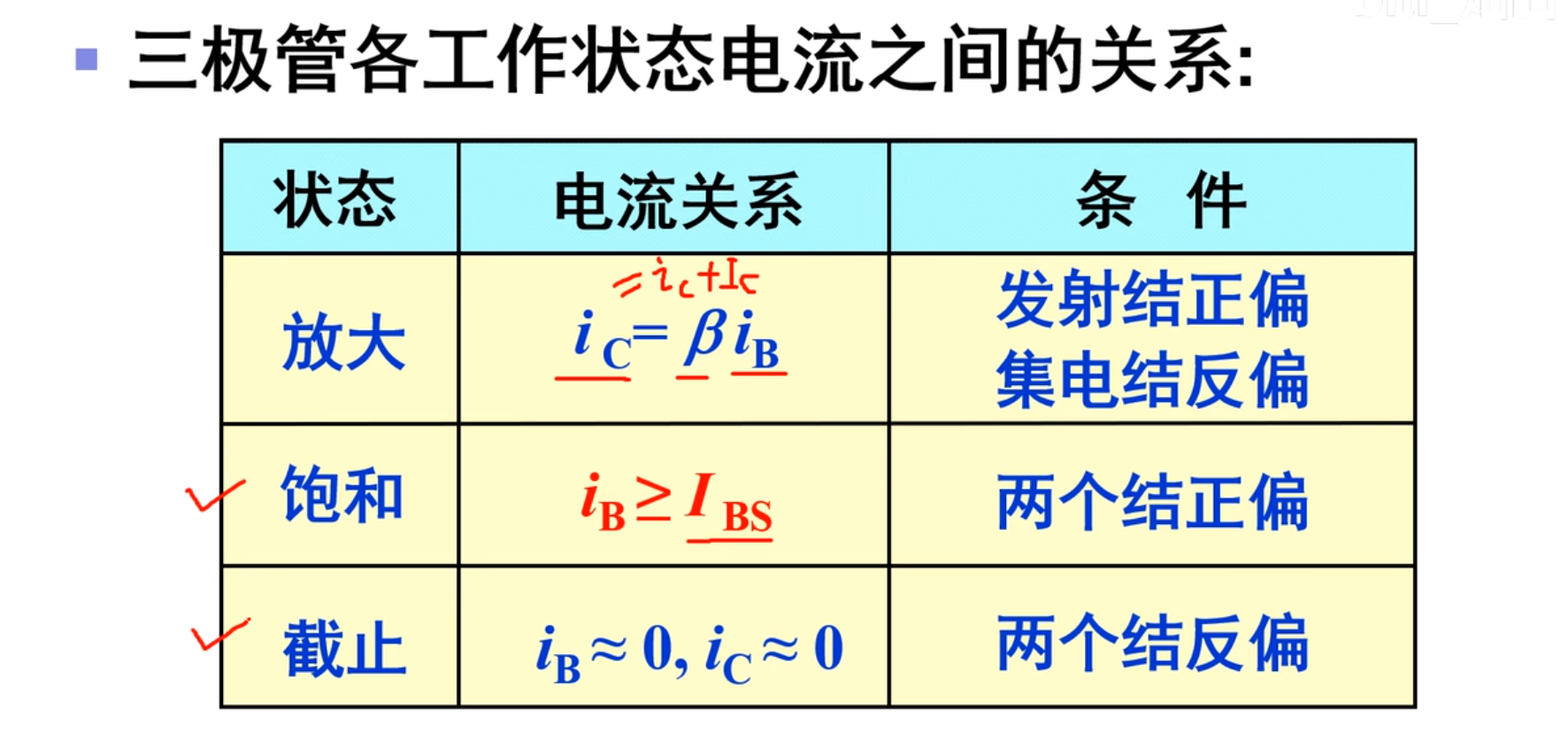

三极管根据两个 PN 结所施加的电压的不同,有四种工作状态:

放大状态:发射结正偏,集电结反偏

截止状态:发射结反偏,集电结反偏

饱和状态:发射结正偏,集电结正偏

倒置状态:发射结反偏,集电结正偏

NOTE

NPN 中,N 的电压比 P 高就是反偏,你负极比我正极大,反了他了

下面进行详细解释:

IMPORTANT

由于三极管有两种形式,所以的状态也都是有两种不同的形式

放大状态

发射结正偏,集电结反偏

上面图中所说的

IMPORTANT

在使用中主要是以

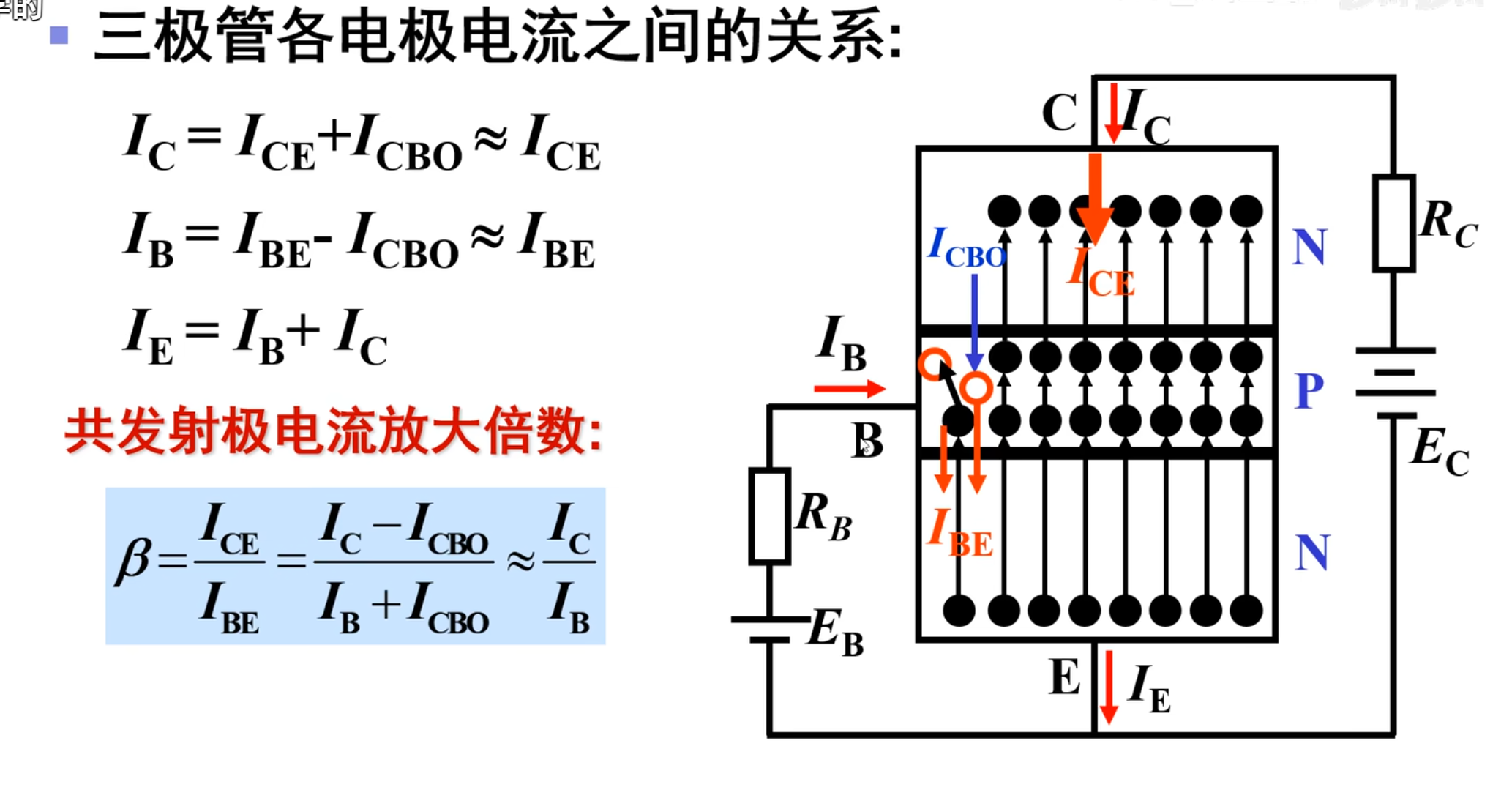

所以,共发射极电流放大倍数是:

所以有:

NOTE

三极管实现了小电流控制大电流,而大电流是

三极管是一种电流控制器器件

上面的部分暂时略过,这部分是三极管的物理实现等一系列问题。

三极管在数电中的应用

首先是三极管的分析:

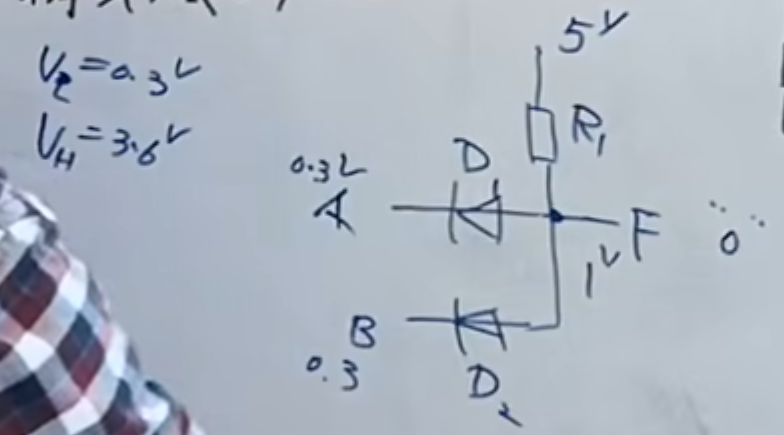

下面图中,假设二极管导通的电压为

假设

然后是一个

在这种情况下,

还有一种情况是

那么

这里就是说明逻辑与是如何使用二极管实现的。

在 TTL 与非门中表示的下面这张图中的内容。

#TODO

这部分还是暂定,到时候哪里不会点那里吧

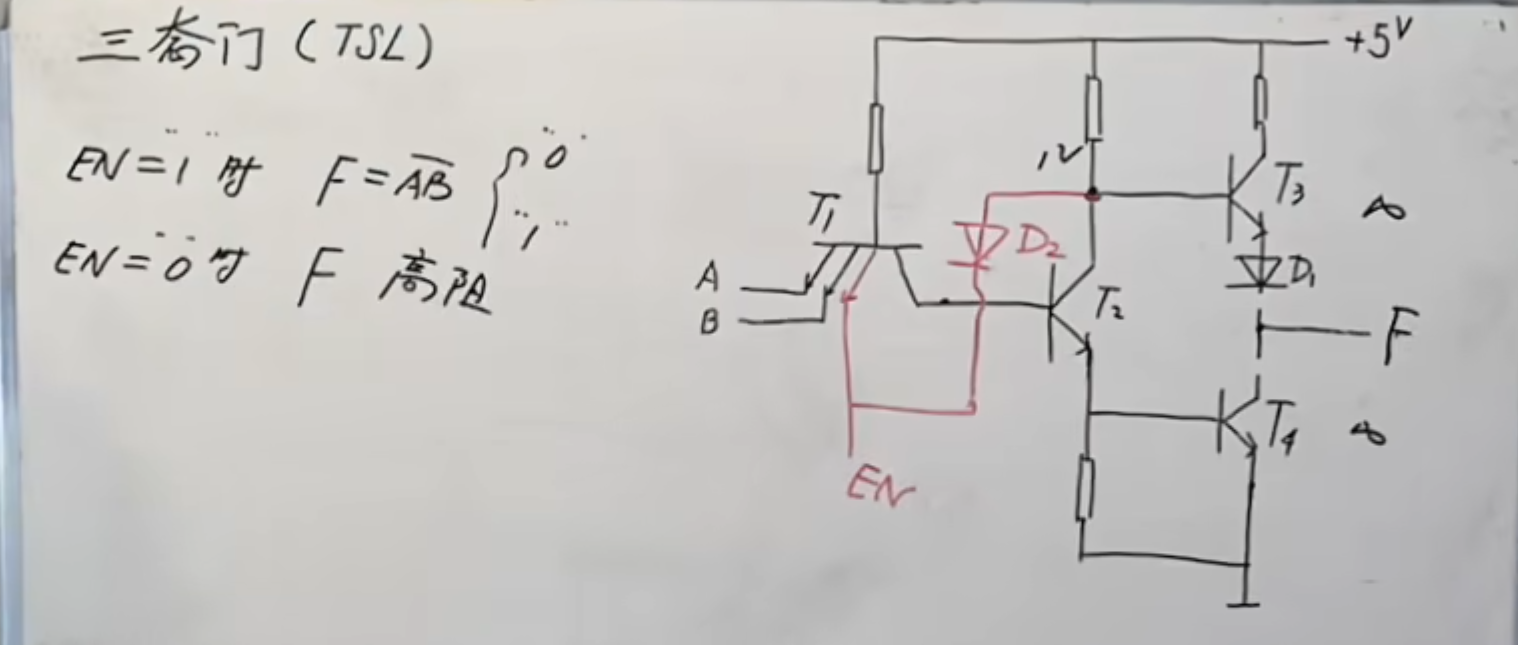

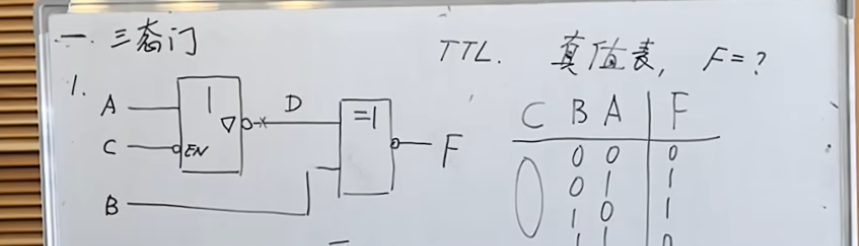

三态门

三态门,主要是指

、

、

其中的

(PS:这里的问题在于不能分析出来为什么会这样,有可能用不到)

这也就导致了一个结果:

NOTE

三态门:

当

当

CMOS 中,如果三态门的使能端是

CMOS 中,如果三态门的使能端是

王海平

王海平