触发器受脉冲变化的控制,这里脉冲的控制,指的就是上升沿、下降沿

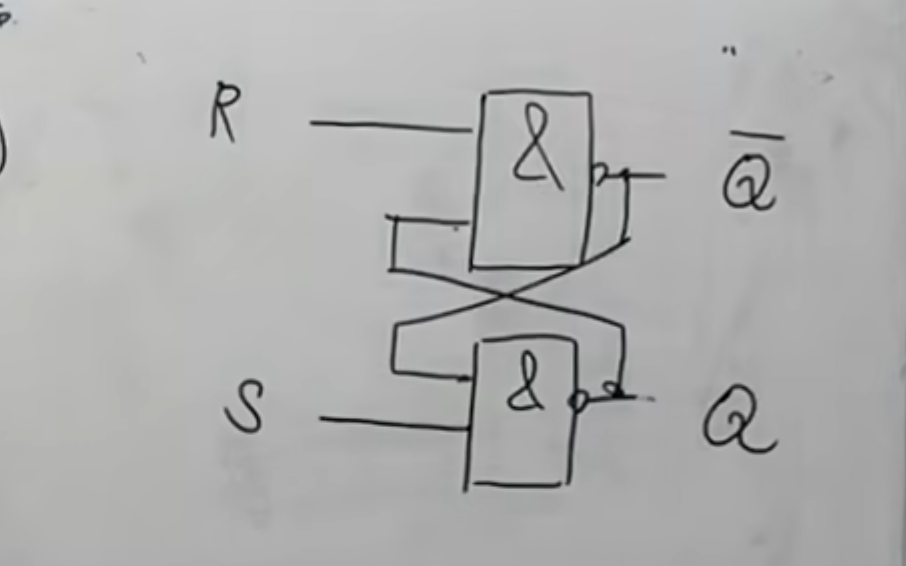

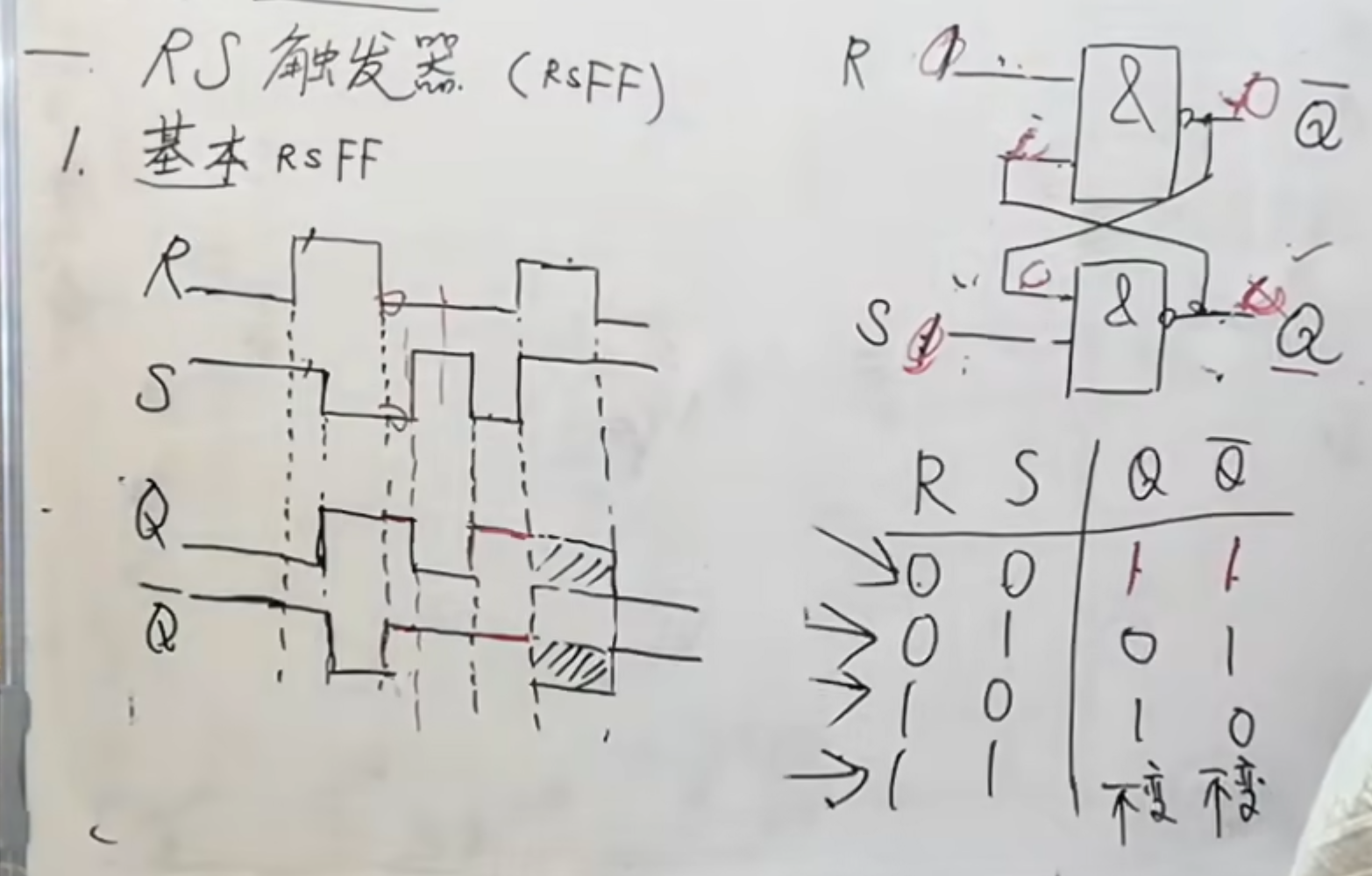

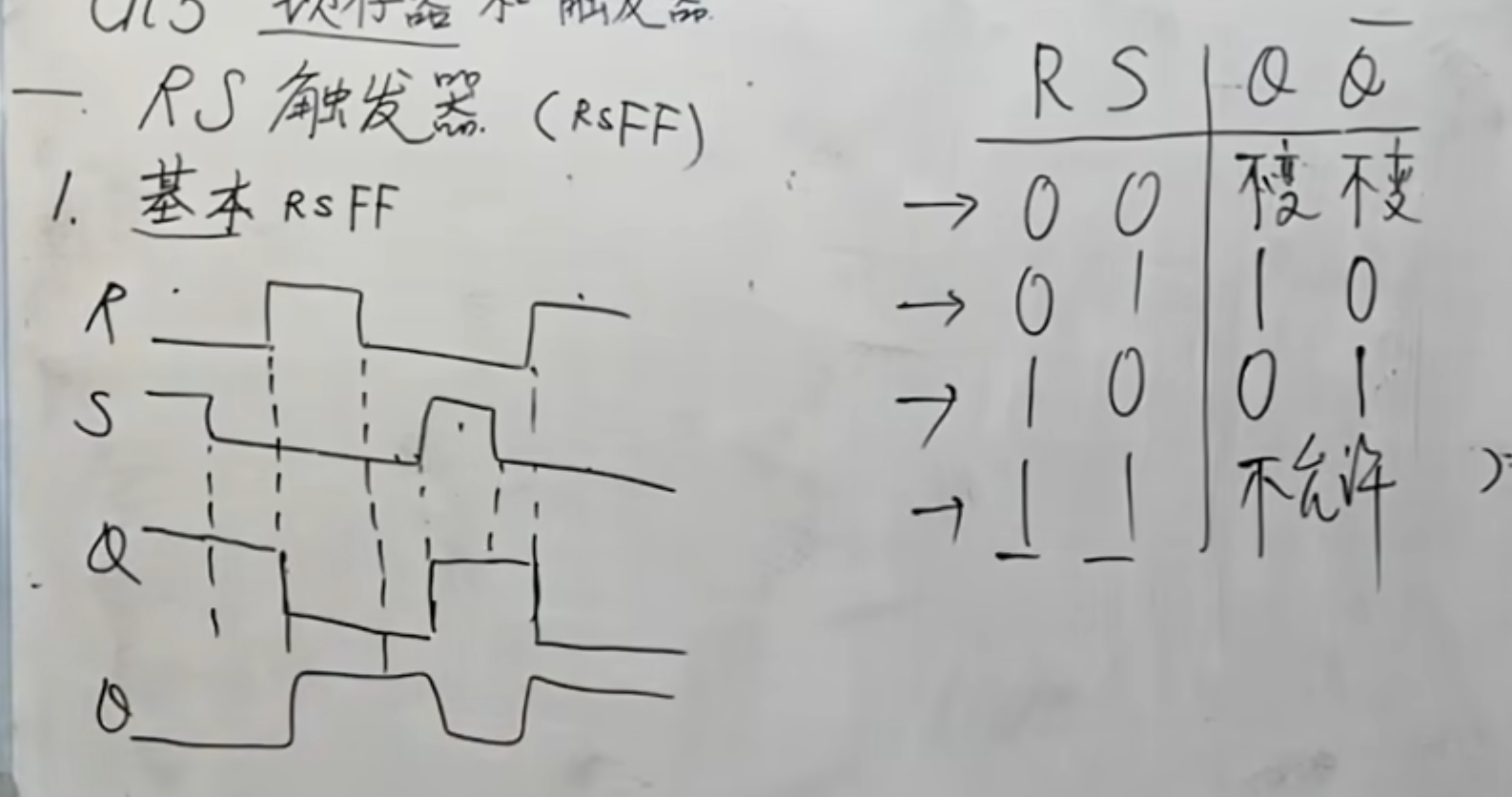

RS 触发器

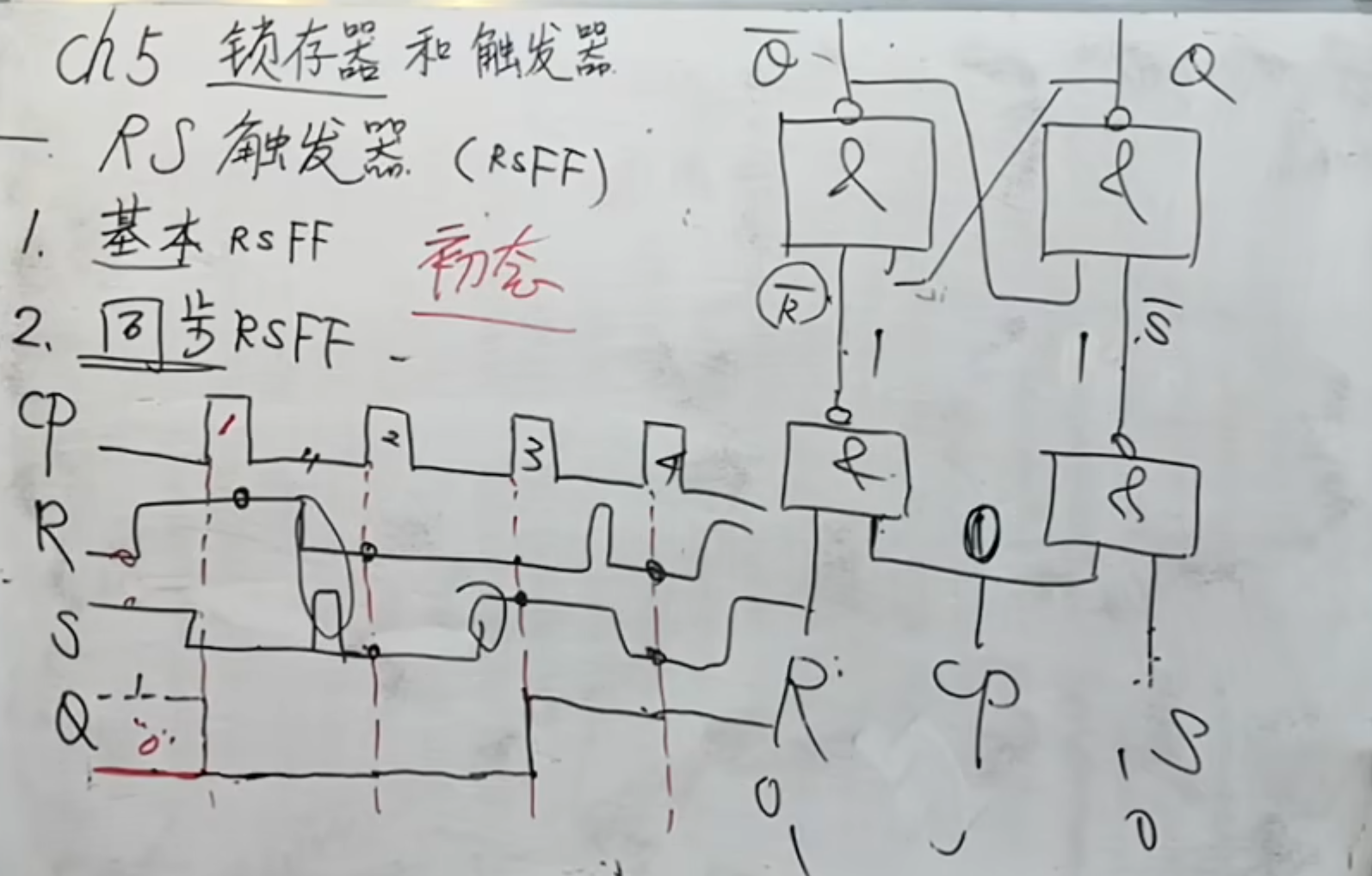

基本 RS 触发器

RS 触发器在正常的工作状态下面,两个输出的状态是互补的。当 RS 触发器的状态是

NOTE

补充:对于与门、与非门来说,

原因在于当与门或者与非门的一端输入为

同理,对于或门或者或非门的一端输入为

主要需要理解的是当

然后最重要的是当

然后再从它的主要功能分析,主要的就是清零和置一。

当

当

当两个端口都有效的时候,是保持不变

但是,我们要避免出现当两个端口都有效的时候(保持不变状态),将两个端口都跳变成无效。这样会导致结果不定(注意,只是在发生跳变的时候会出现这种不定的情况,但是如果只是两个输入都是无效的,是按照真值表正常输出的。)

上面的是低电平有效,实现的是与非门,如果是高电平有效,那么实现的是或非门。

NOTE

有的时候,题目上给的图即是

主要,这里不是抵消的意思,无论是一个非,还是两个非,意思都是低电平有效。而不是抵消,硬要说的话,可以认为是这两个部分进行相或。

一个非就是非,两个非也是非,只有都不是非才是真。

下面实现的就是或非门。逻辑和与非门是相反的:

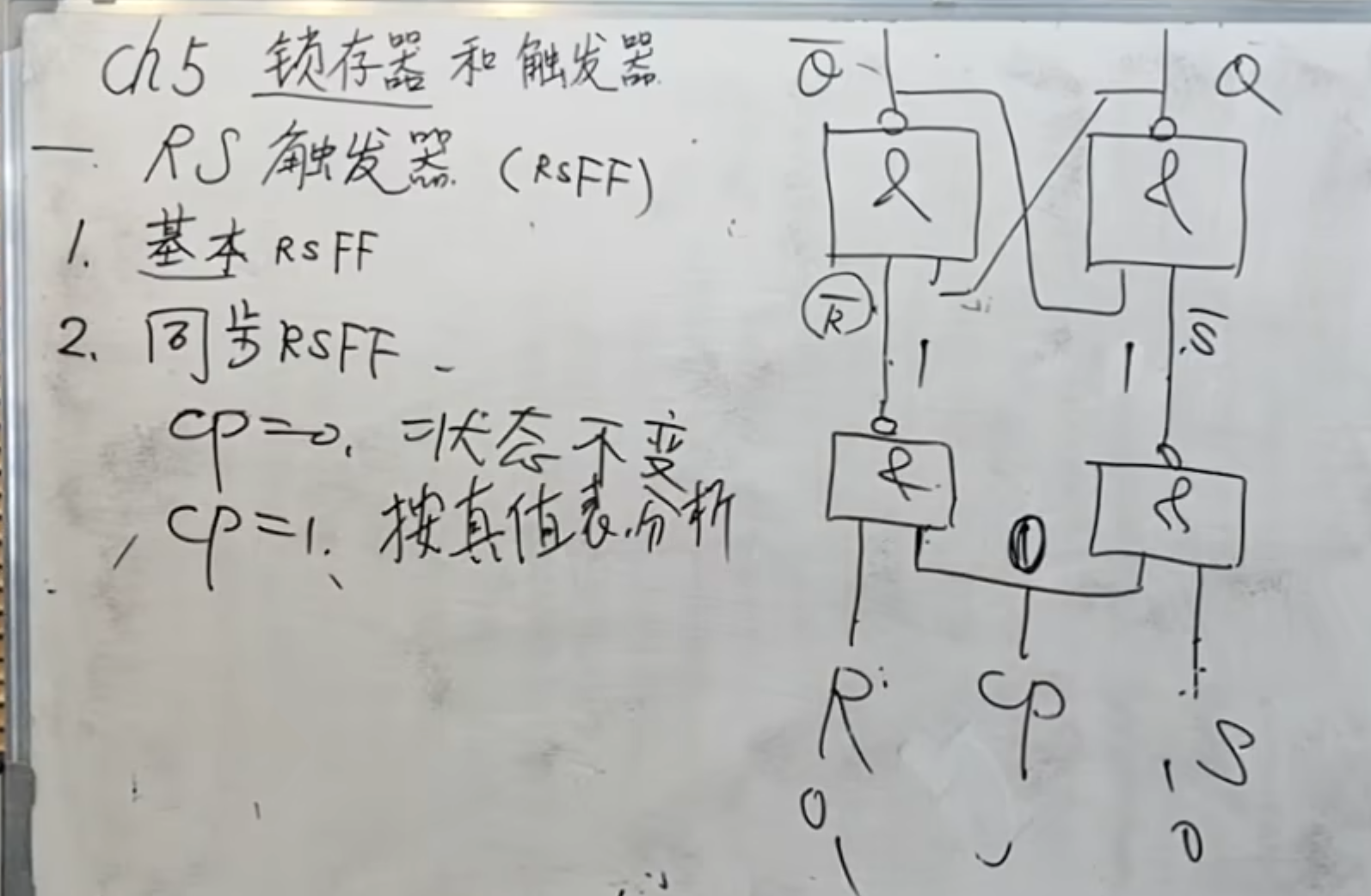

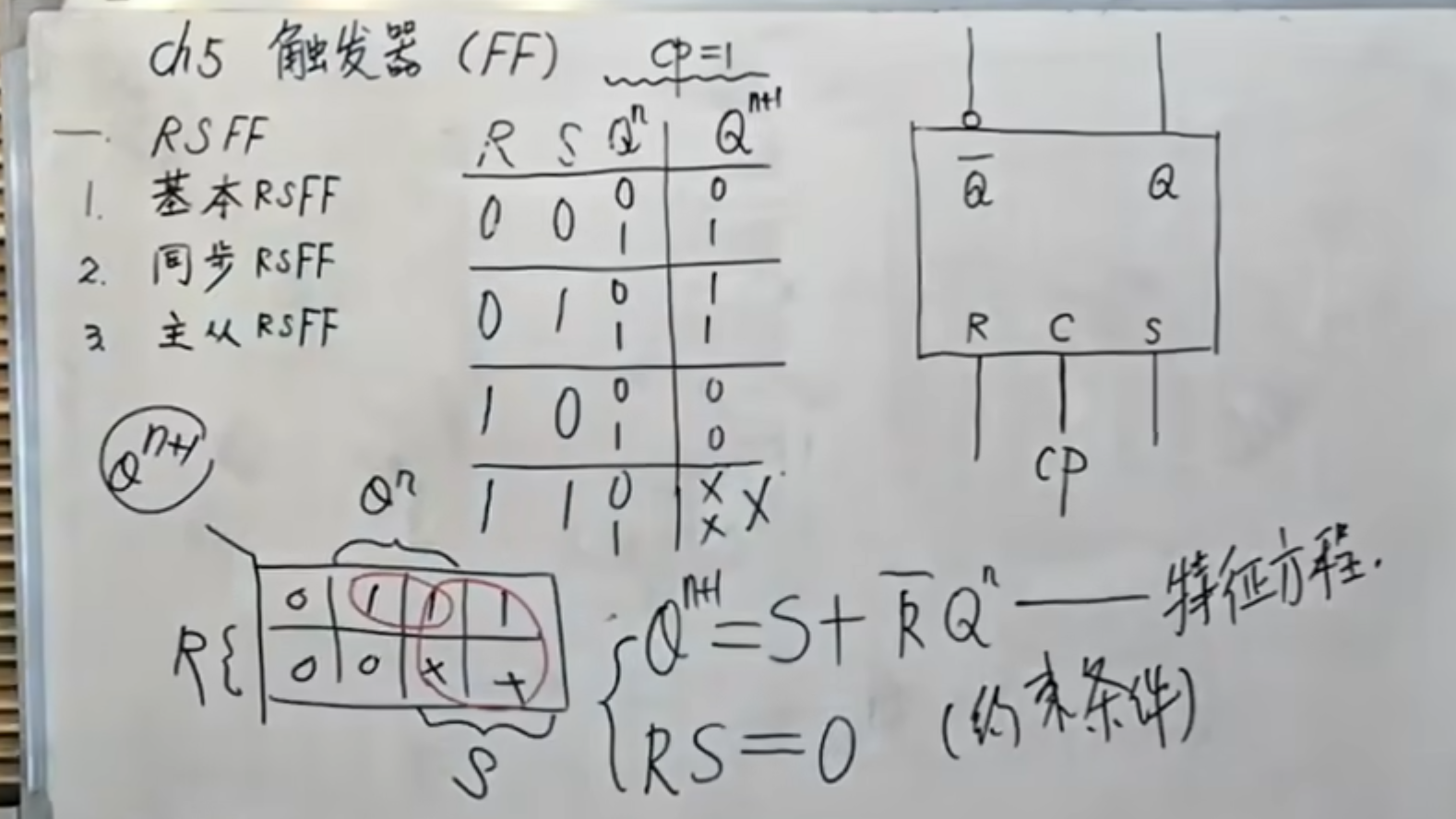

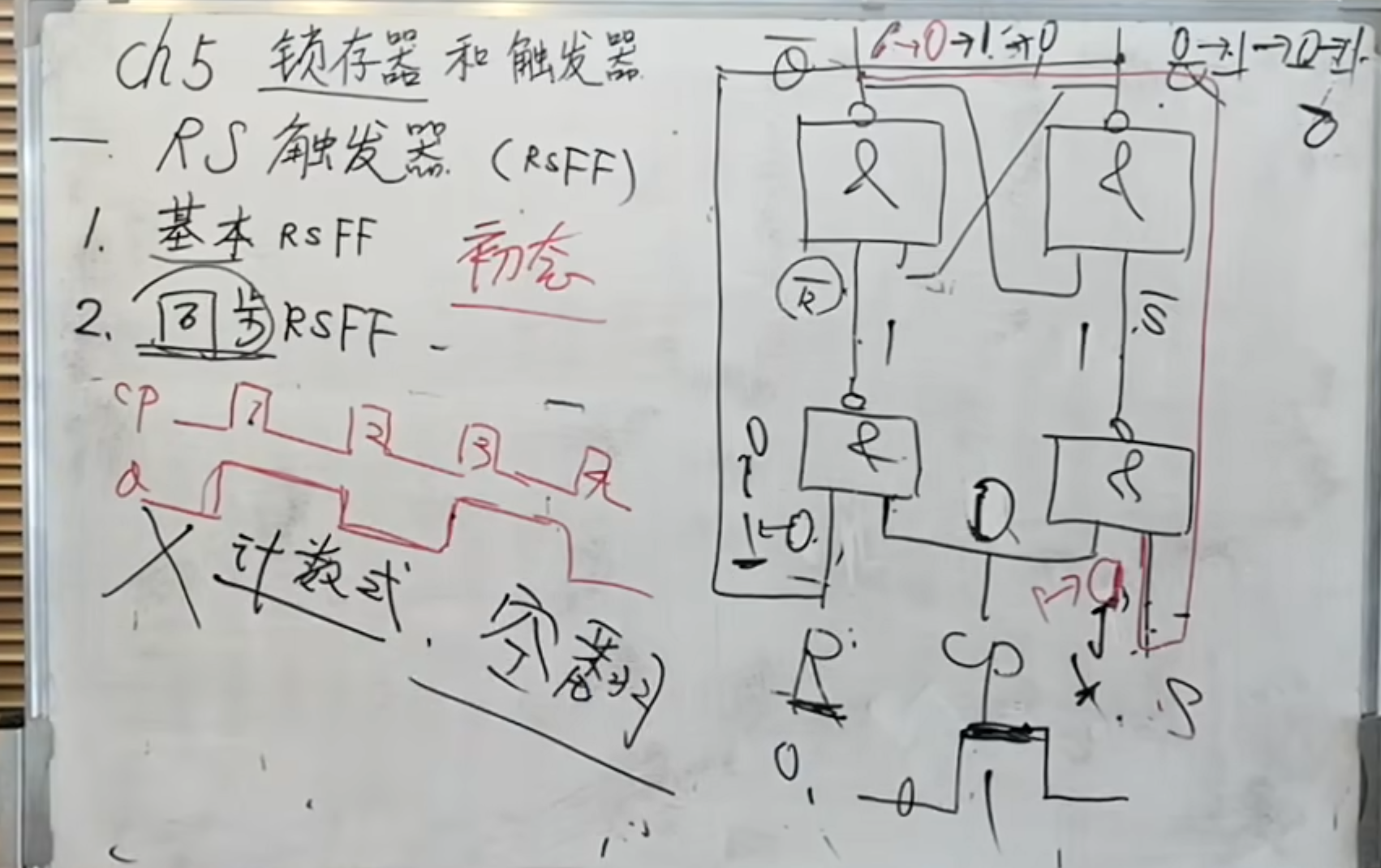

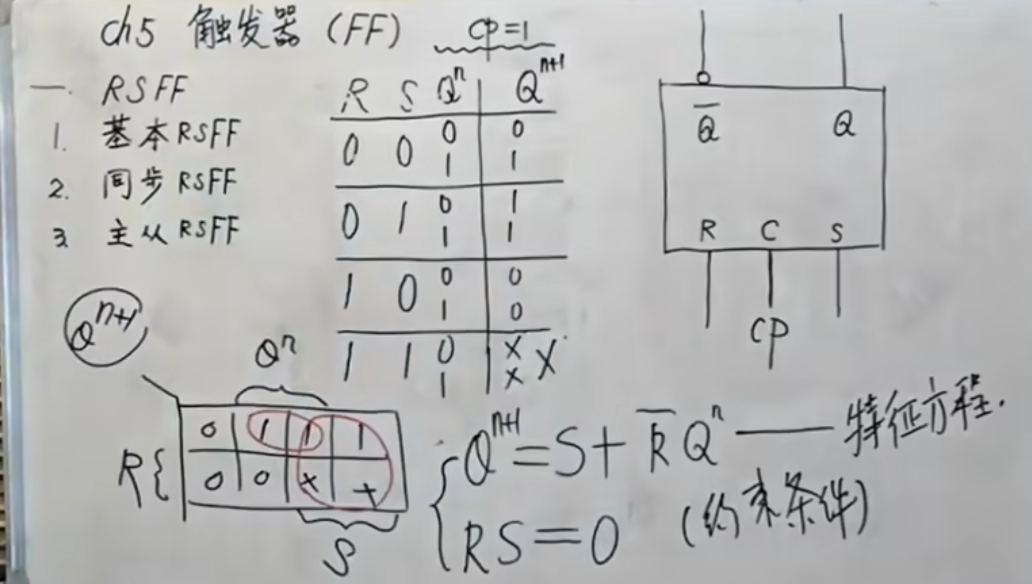

同步 RS 触发器

同步 RS 触发器主要解决的问题是在基本 RS 触发器中,当

为了避免基本 RS 触发器出现的问题,实现的方法主要是利用前面的时钟脉冲

当

只有当

实现的真值表在下面图中所示:

注意,上面的真值一定是当

其中,我们通过分析真值表,可以得到:

当然,约束条件是:

也就是

然后,如果我们将输出再接回输入:

理论上会出现来一次

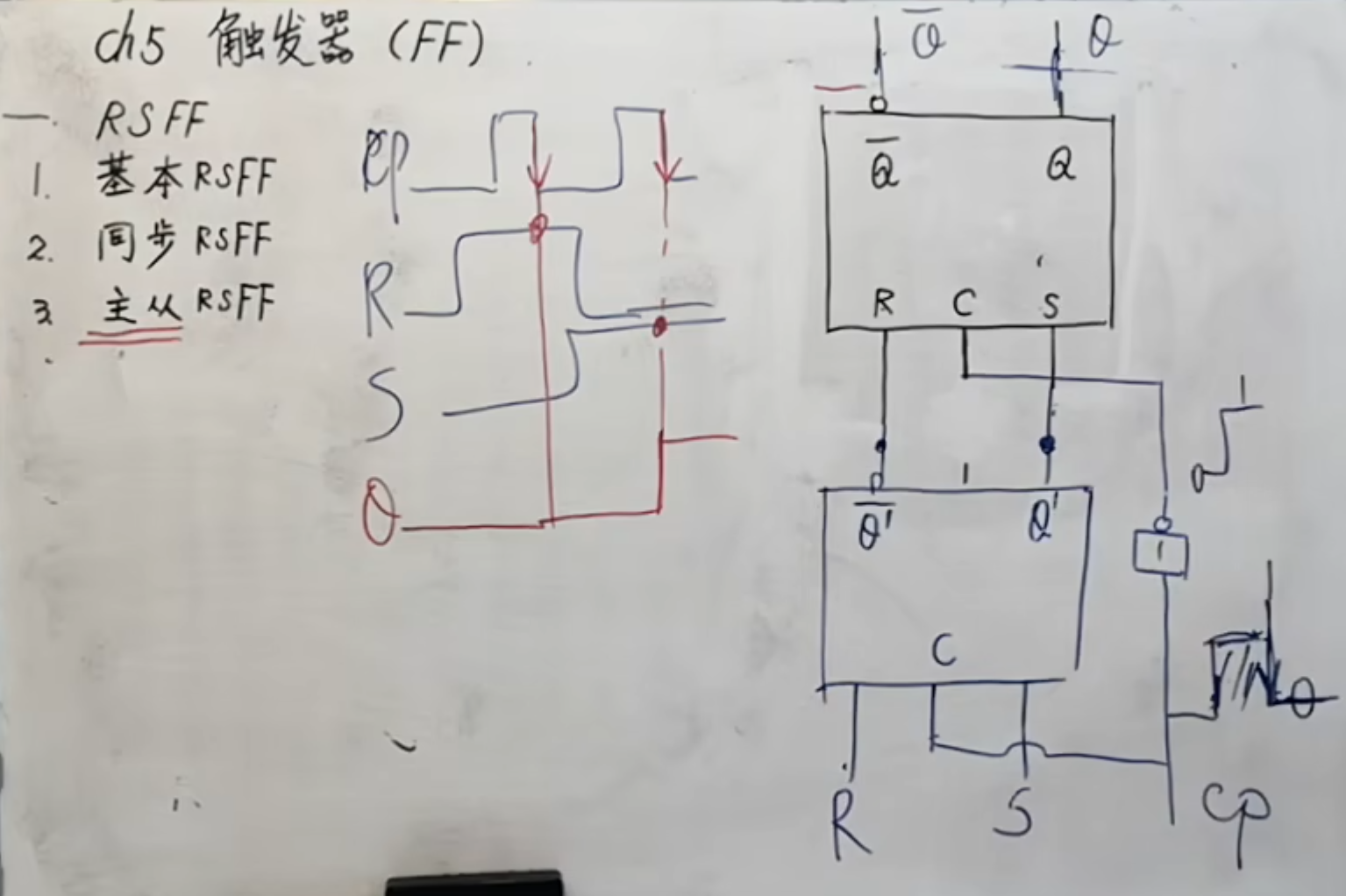

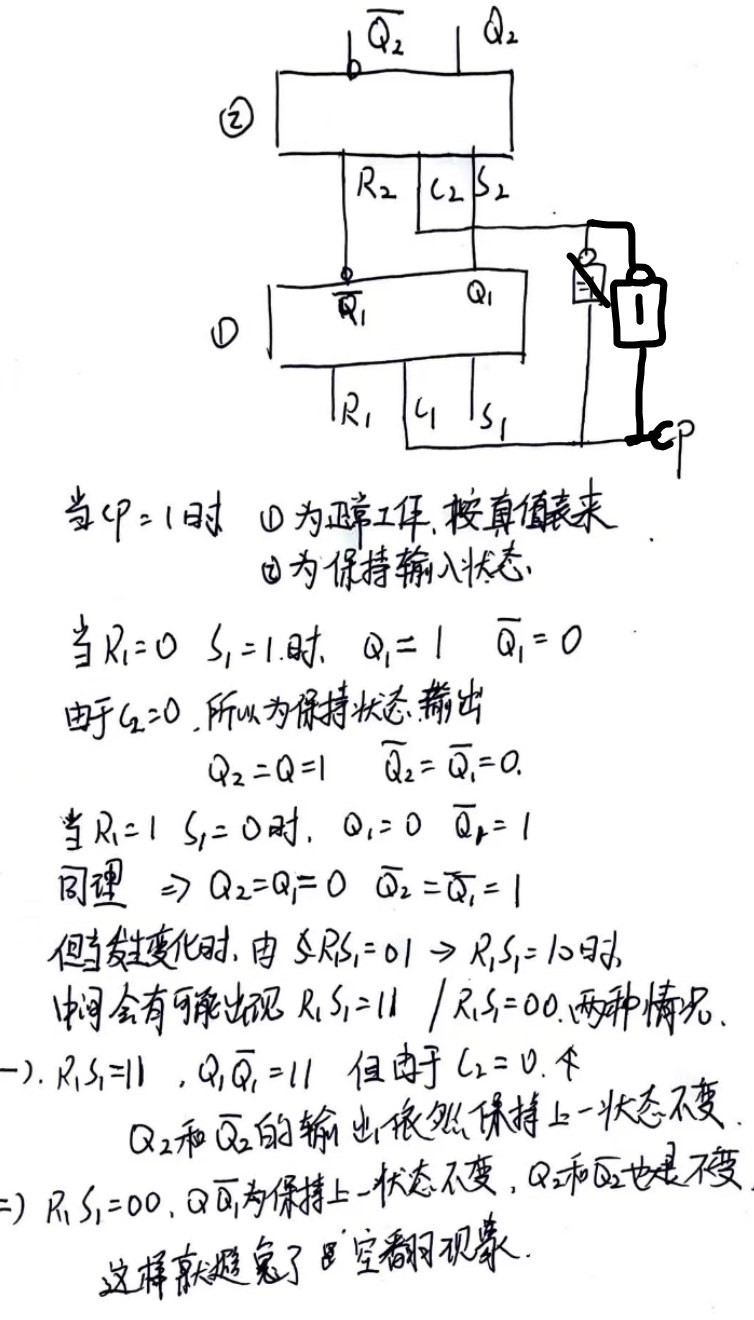

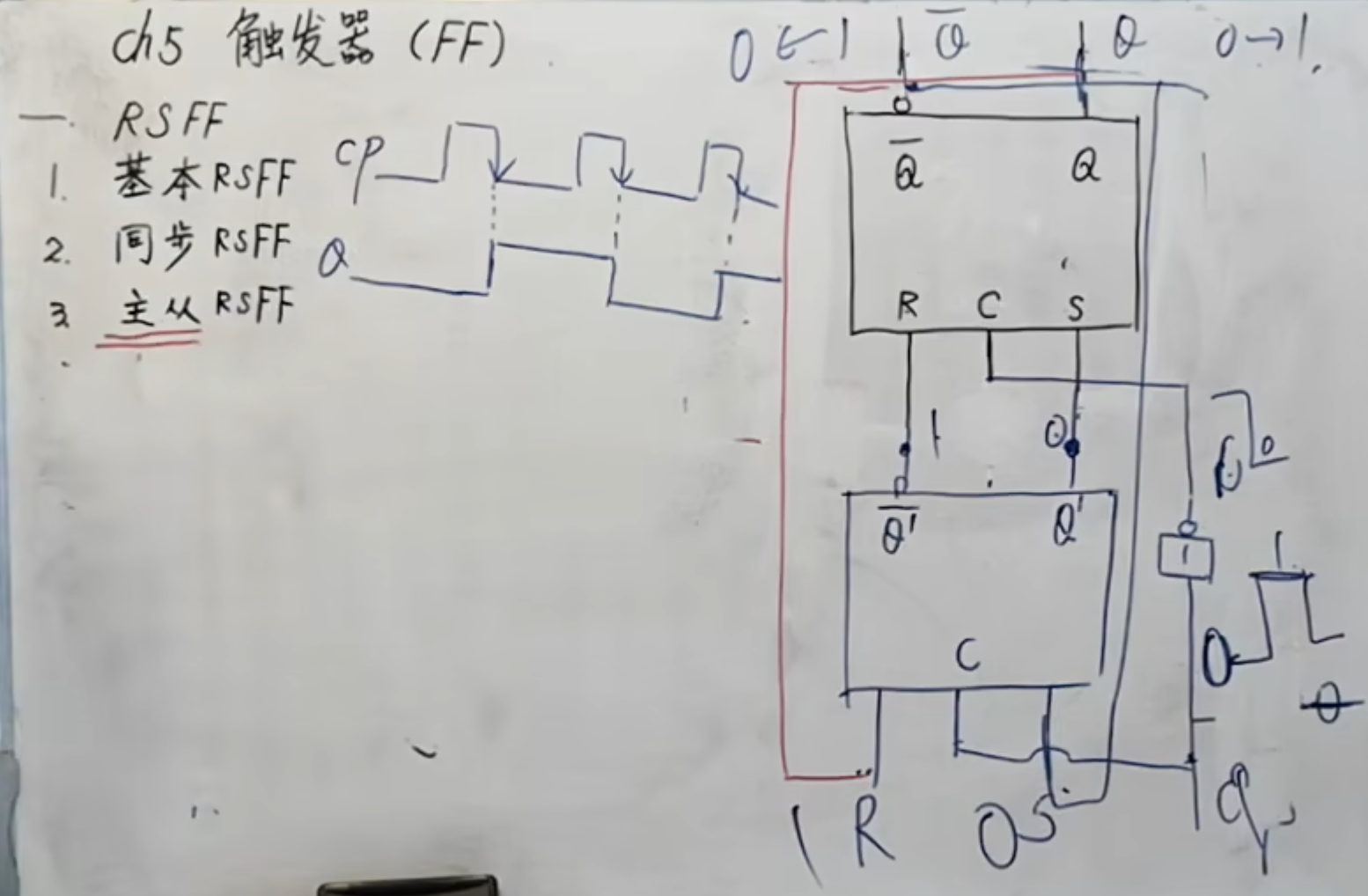

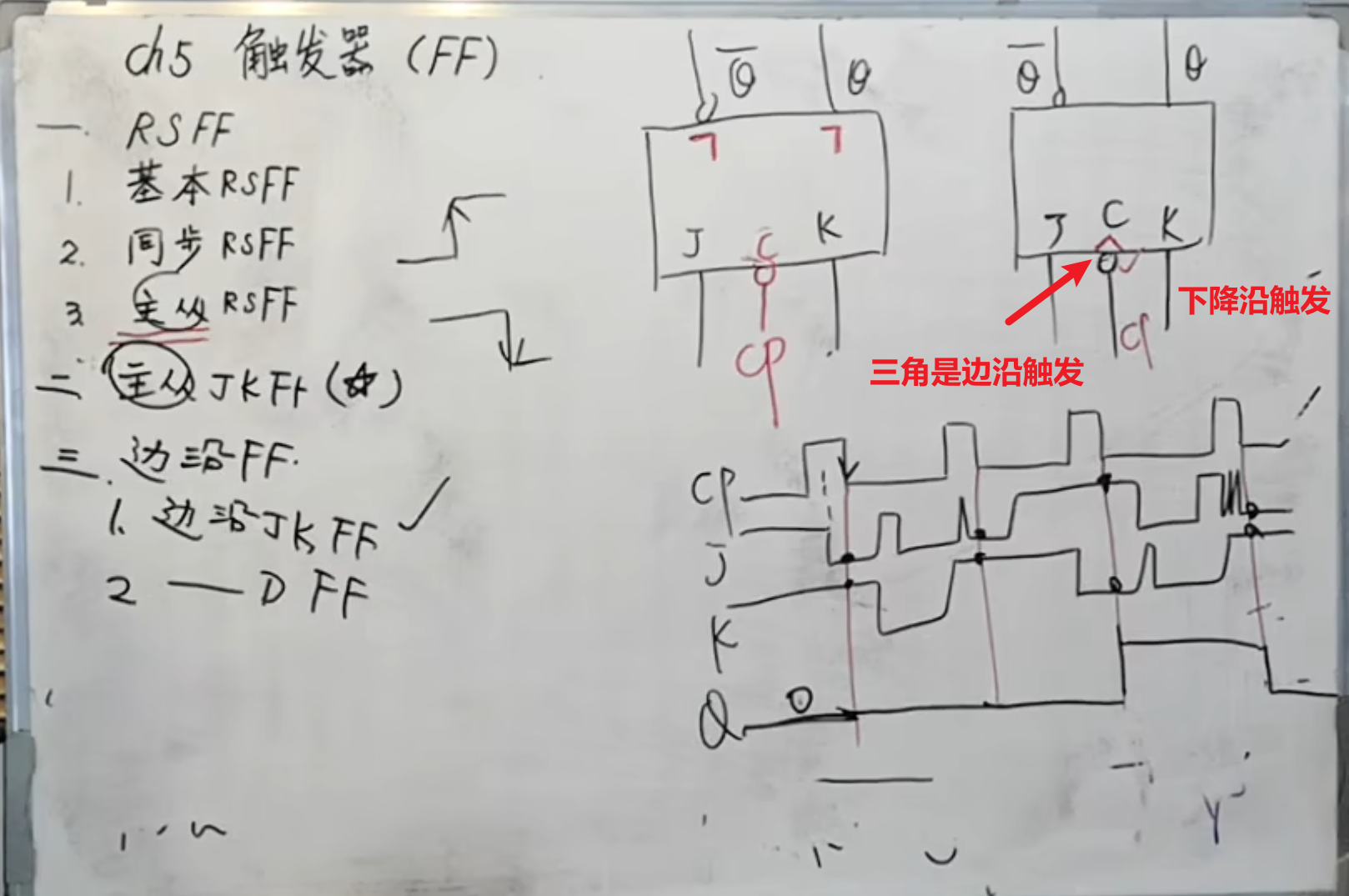

主从 RS 触发器

主从 RS 触发器,顾名思义,肯定是由两个触发器组成。具体接法如下所示。

IMPORTANT

主从触发器一定是在下降沿的时候才进行激活功能。

这种结构就避免了空翻现象。

下面进行分析:

如果是将主从 RS 触发器的输出再接到输入上,那么它的输出

但是,无论是上面的那种 RS 触发器,总有一种情况是不被允许的。

低电平有效的,不允许

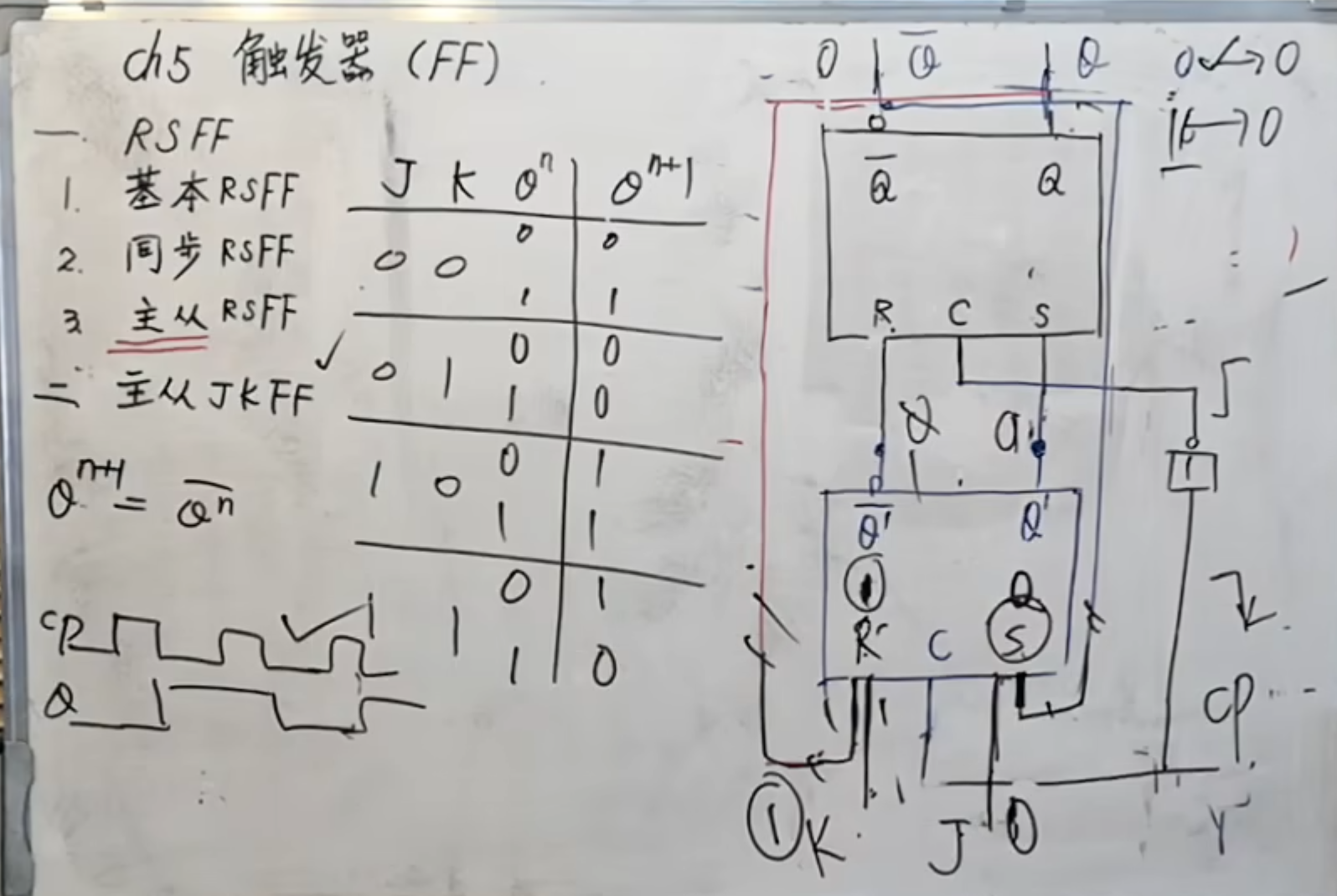

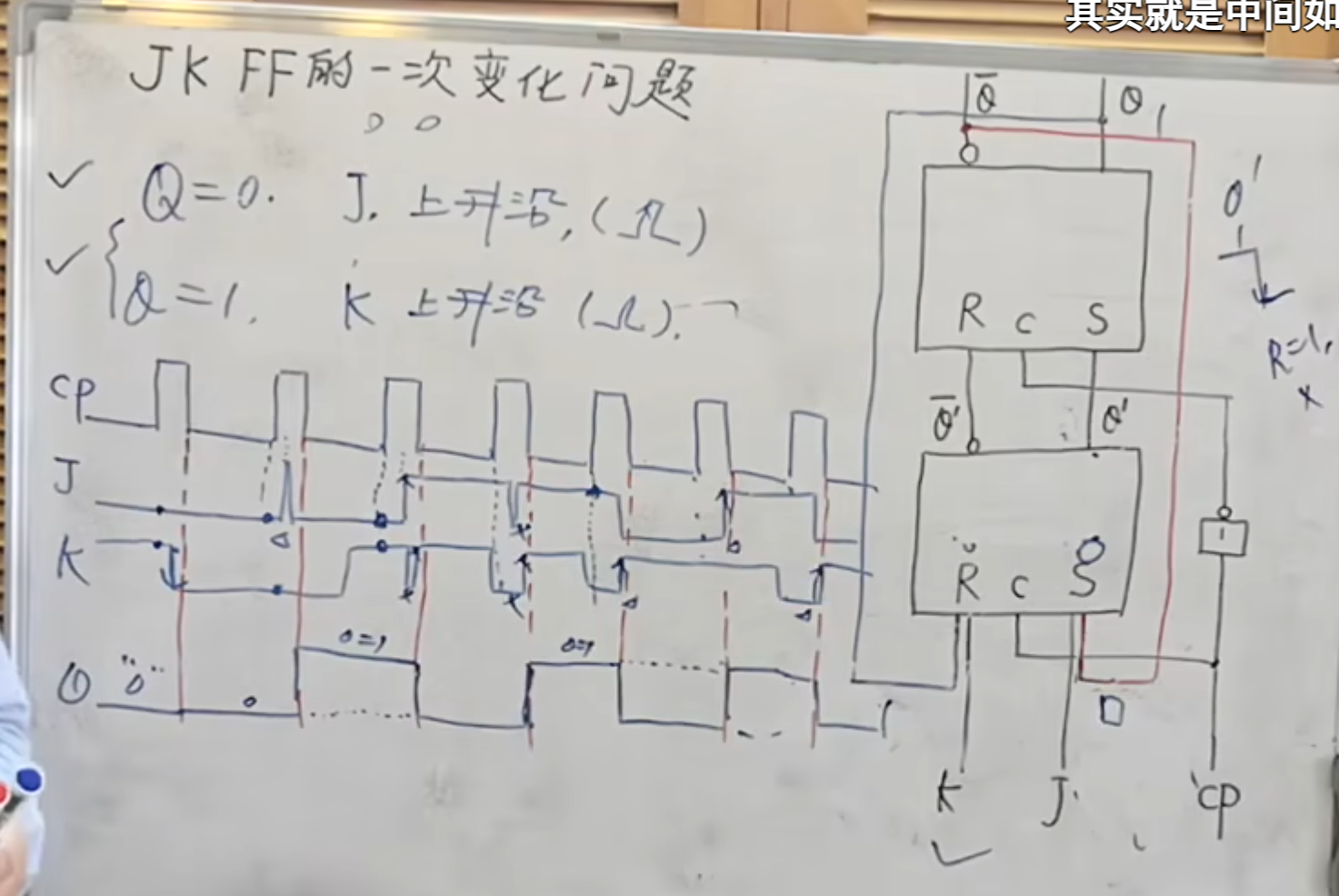

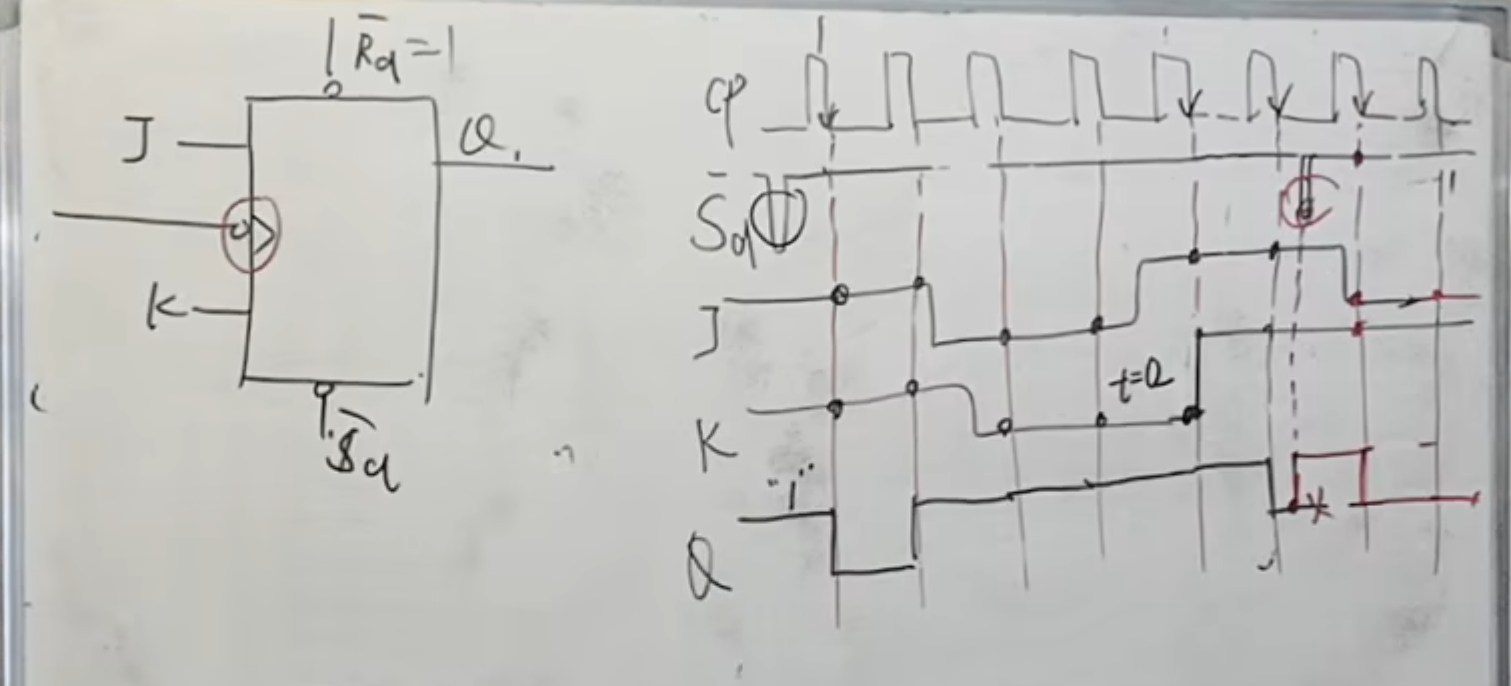

主从 JK 触发器

本质上,对于 RS 触发器的输入是可以不只一个输入的,可以有多个输入。利用这个设计,以及为了解决上面 RS 触发器的问题,在主从 RS 触发器的基础上利用两个

可以看到它是在主从

NOTE

这里的分析不是很难,但是比较麻烦。后续如果有需要再来分析。

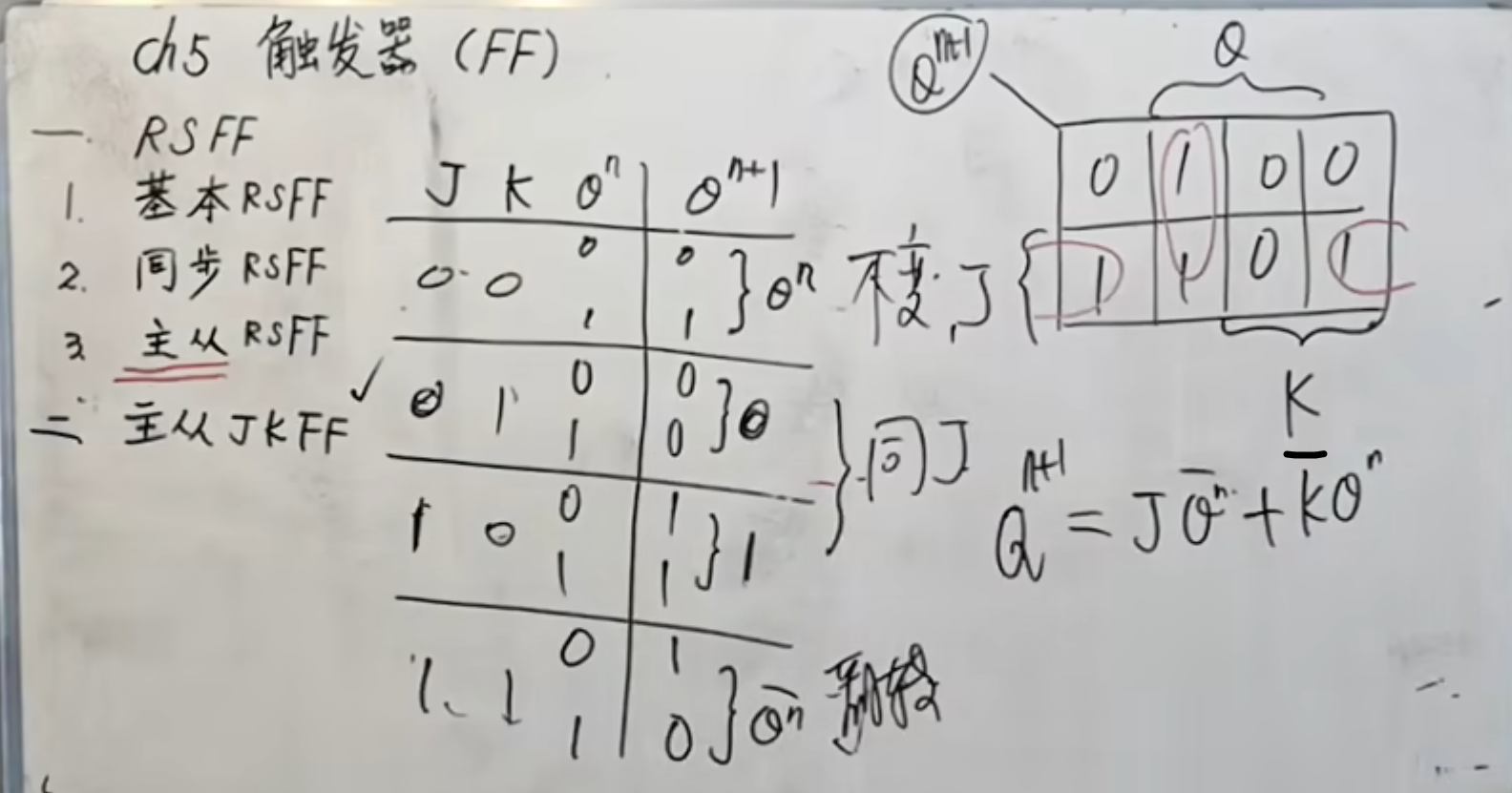

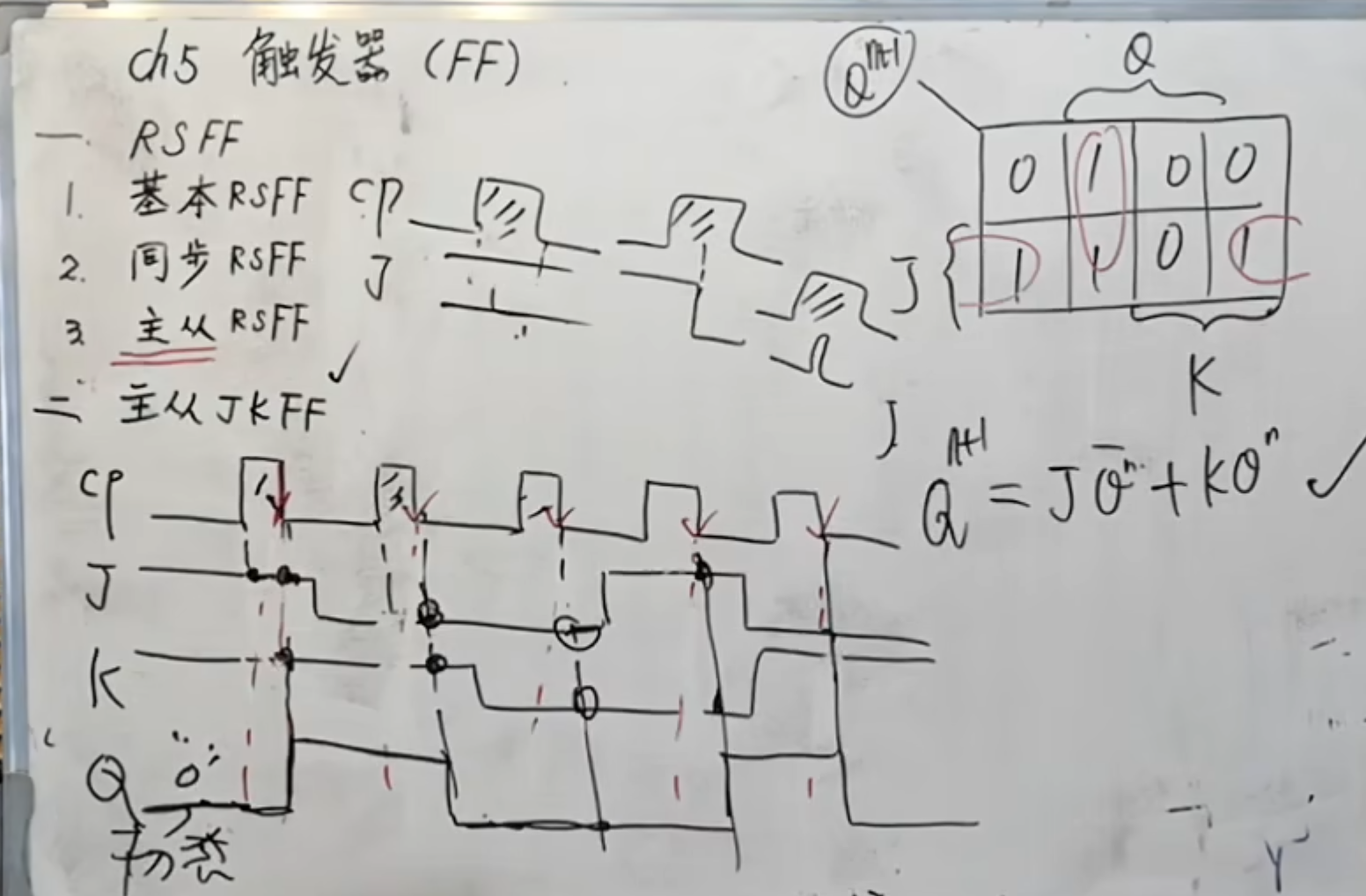

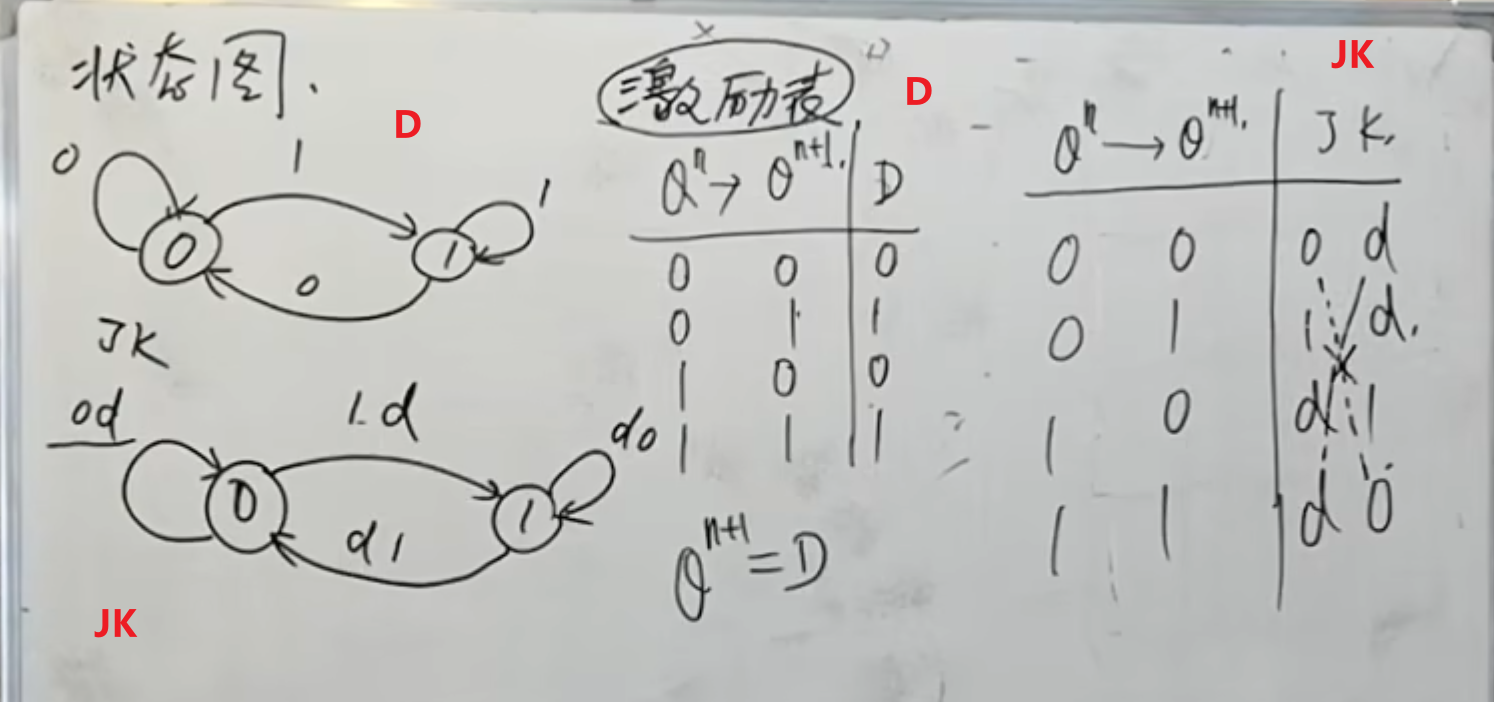

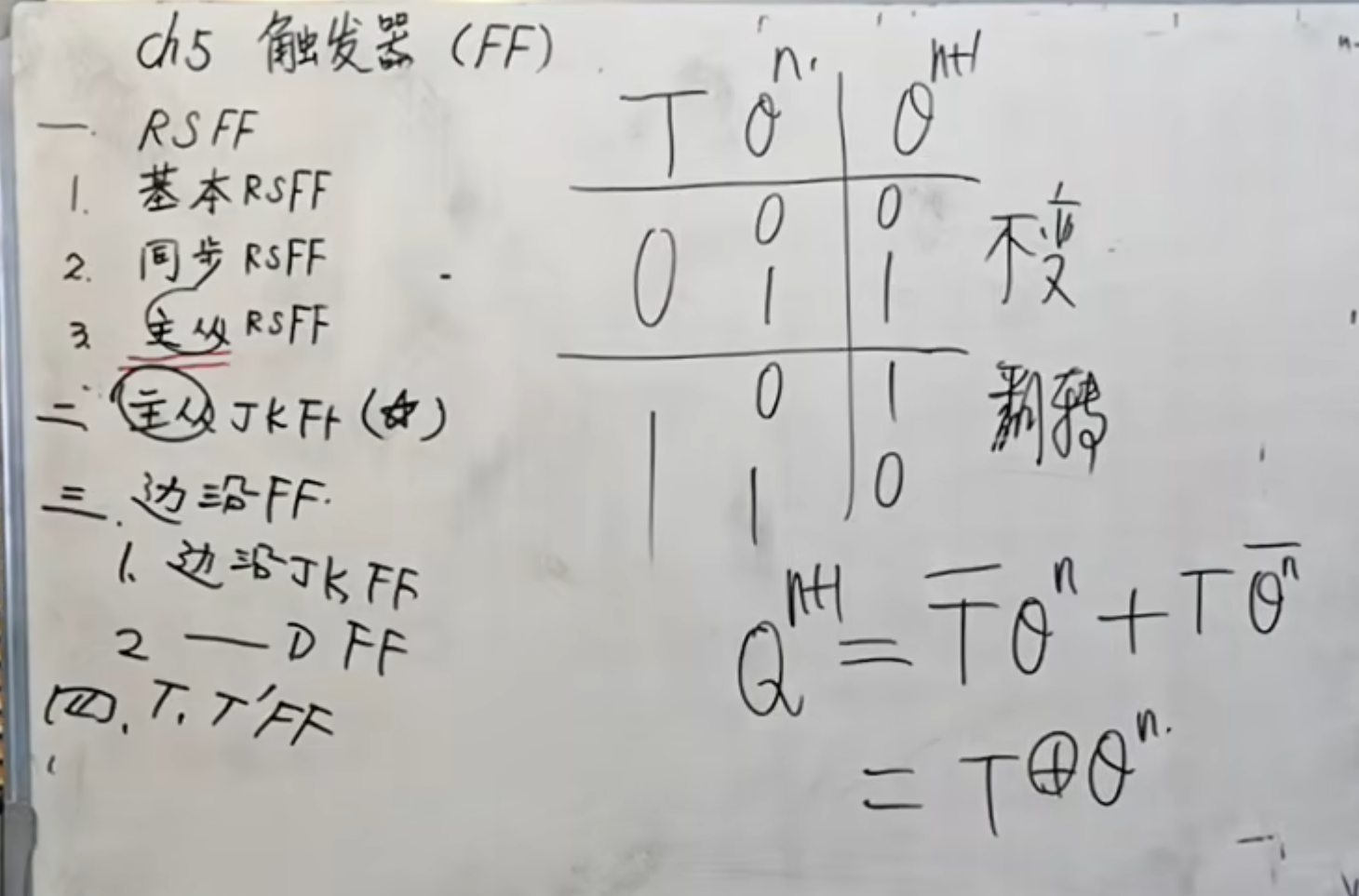

关键在于记住这个主从 JK 触发器的真值表:

IMPORTANT

记忆口诀:

下面根据真值表,分析出它的特征方程:

特征方程:

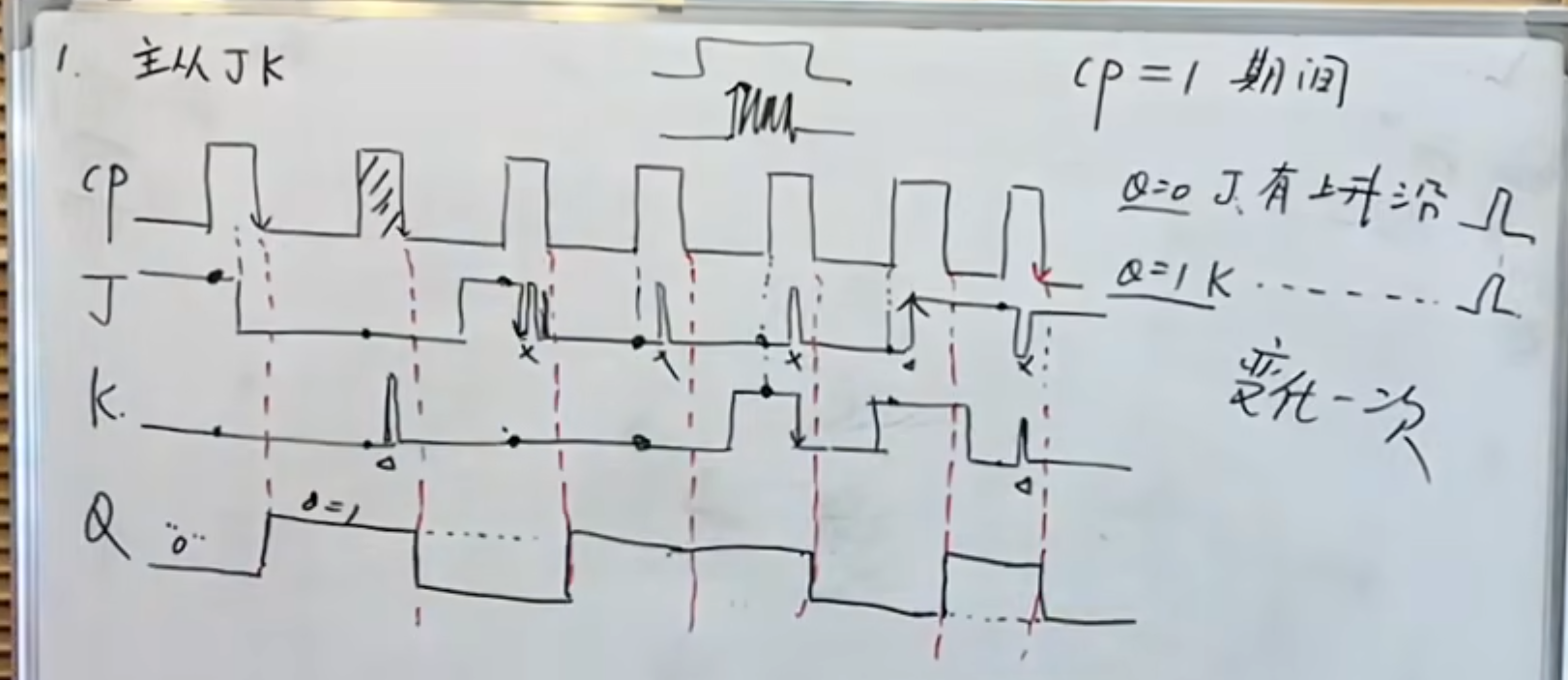

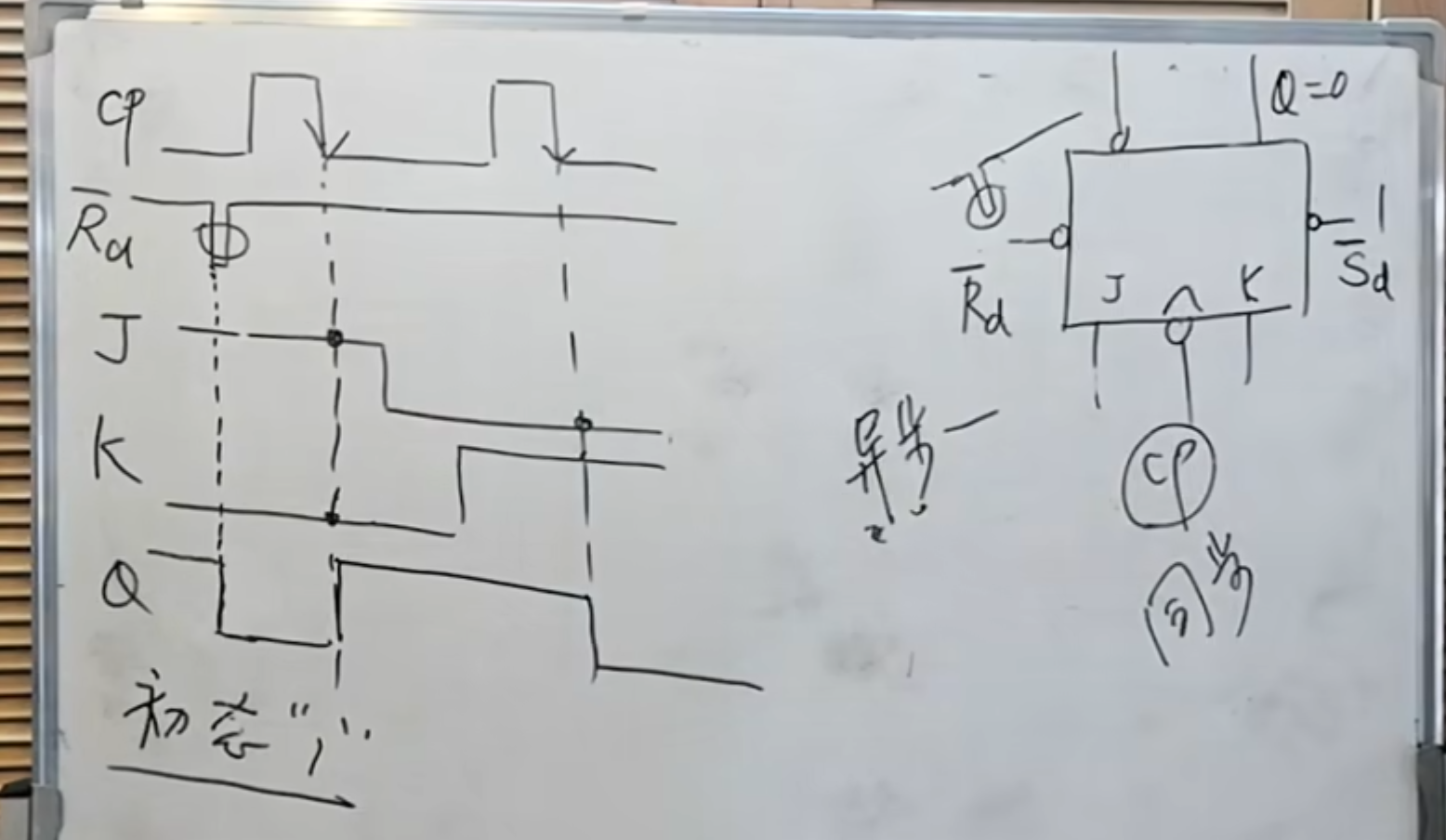

核心就是记住口诀,下面是一个例子:

IMPORTANT

注意,是

意思是,尽管要在下降沿的时候翻转,但是怎么翻,或者不翻,都要看上升沿发生的时候,

此外,当

IMPORTANT

注意,上面的波形分析是基于在

后面会补充会发生什么

NOTE

当

接下来就分析,当

当一开始

那么当

但是如果

解释看真值表:

而

下面是例题以及总结:

NOTE

当

当

上升沿必须优于(早于)下降沿才会导致结果翻转,如果下降沿先发生(在同一个

在上面图中的第三次

再来一个例题:

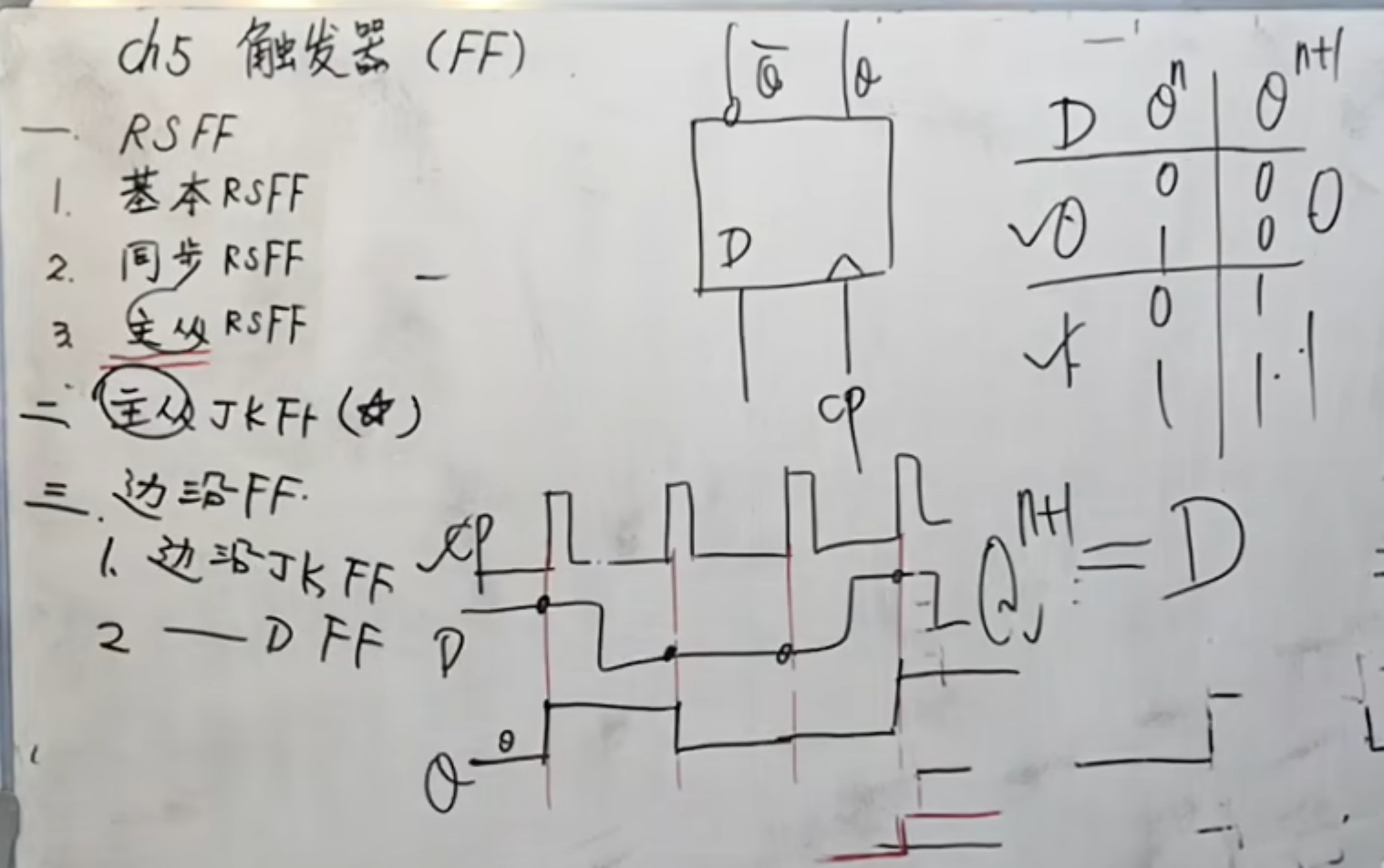

边沿触发器

下图是分别是

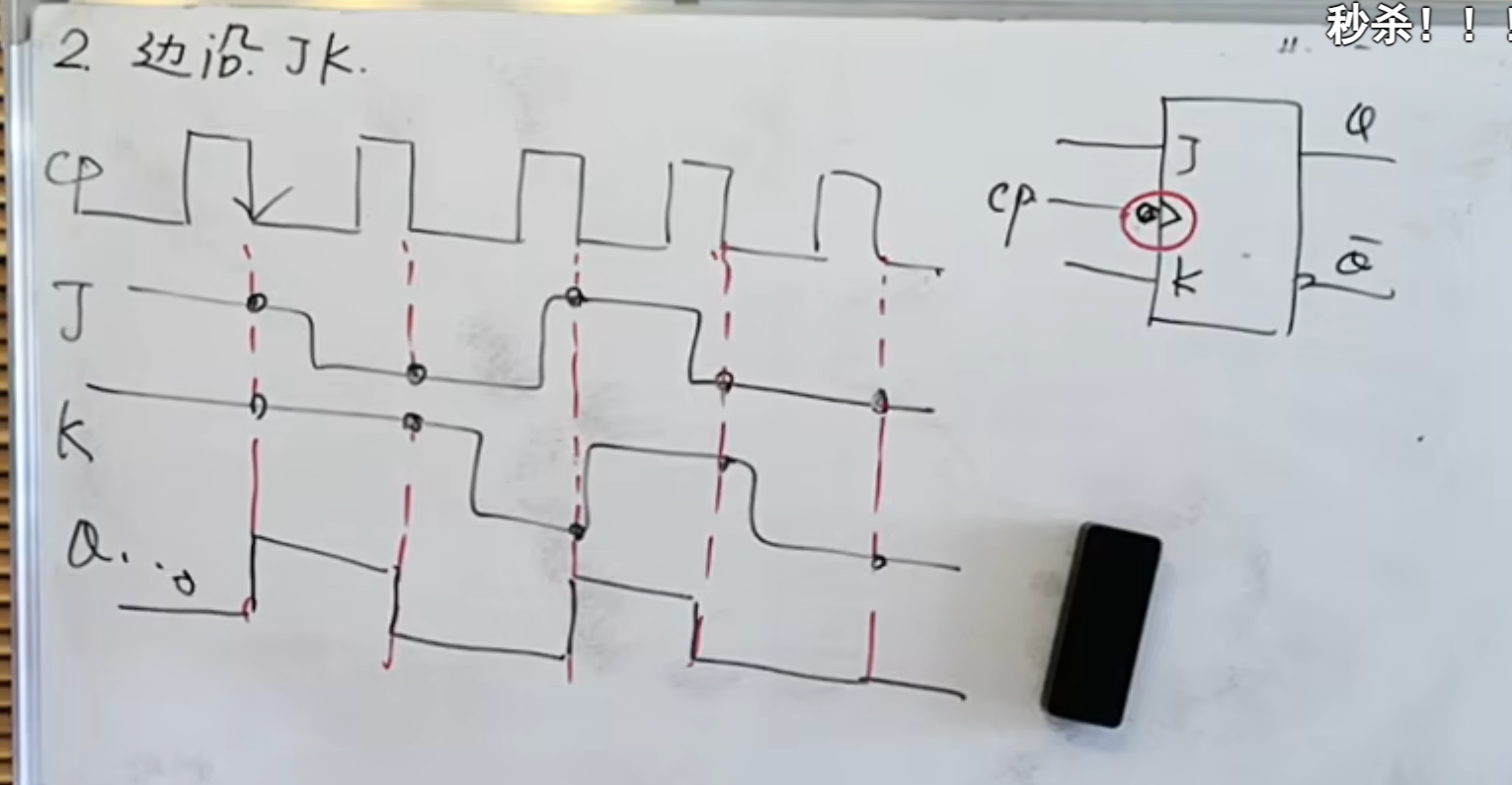

边沿 JK 触发器

由于

NOTE

在一些题目中,需要注意符号问题,当

边沿

对于边沿

之前对于初始条件,一般是将其做为

注意看,在图中,依然是低电平有效,所以在使用中,除了要强制清

此外,因为是低电平有效,所以它还是在下降沿触发。此外还要注意的是,由于平时都是

NOTE

当然,有异步就有同步,同步是要和

举个例子来说明:

NOTE

如果出现下降沿和

那么这个时候,我们一般认为它是按照前一瞬间(在这里是

一道例题:

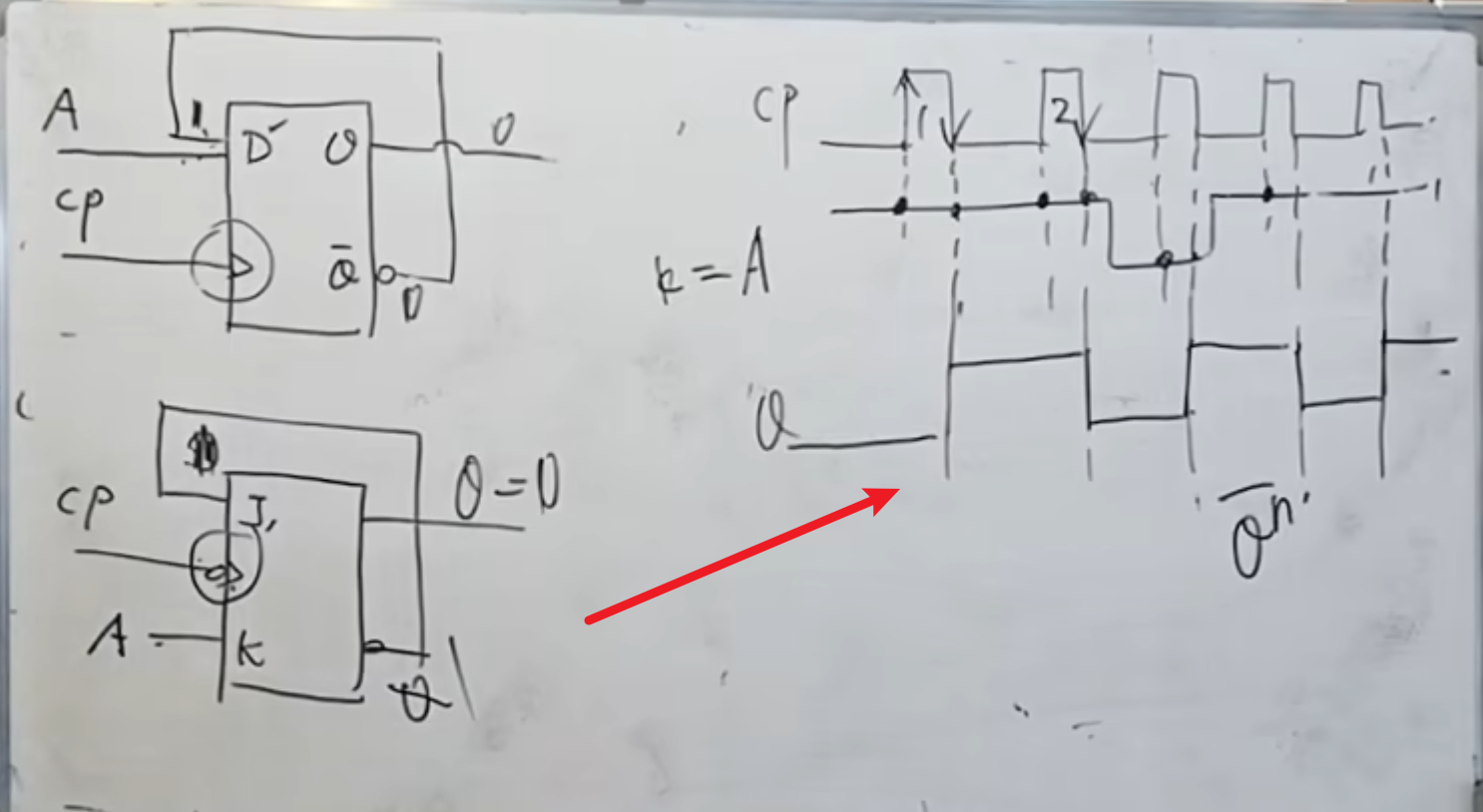

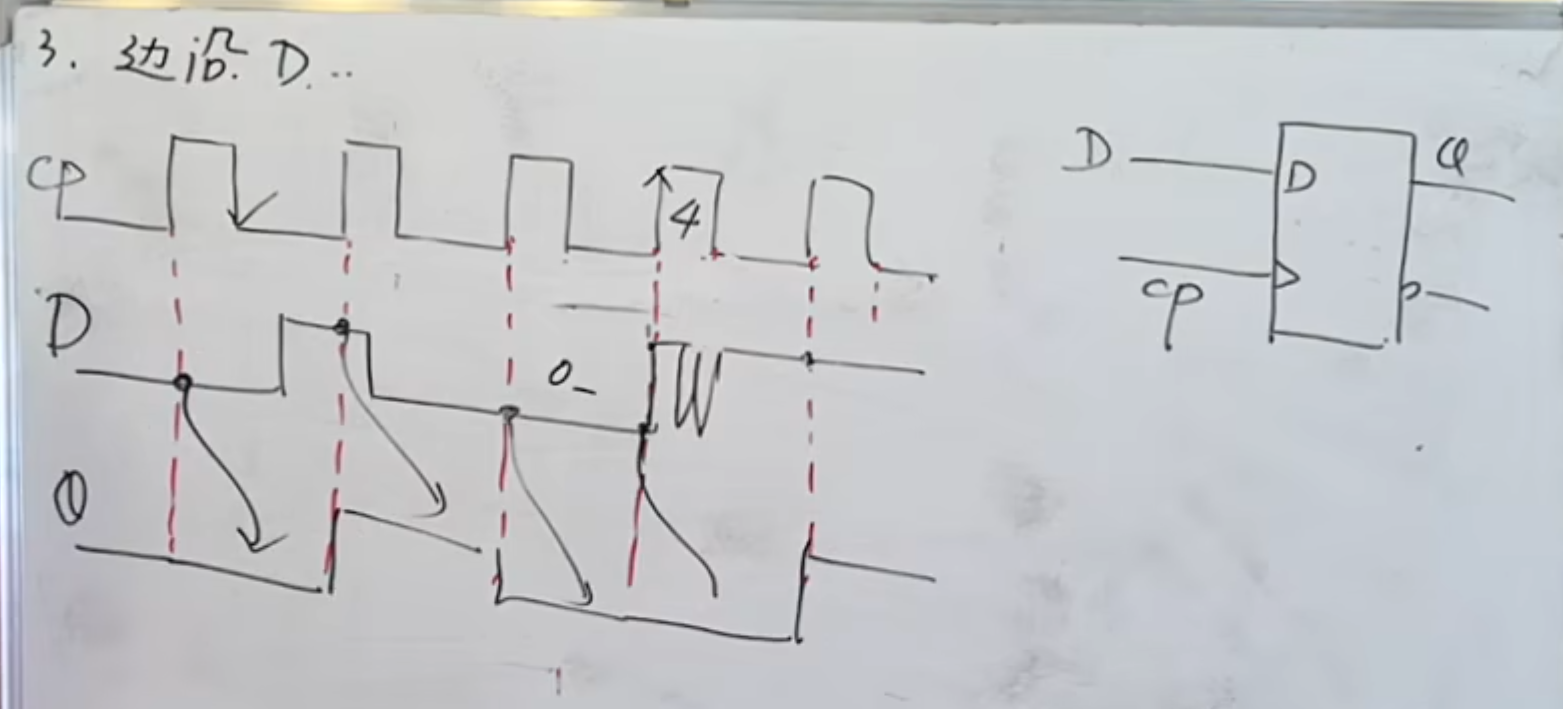

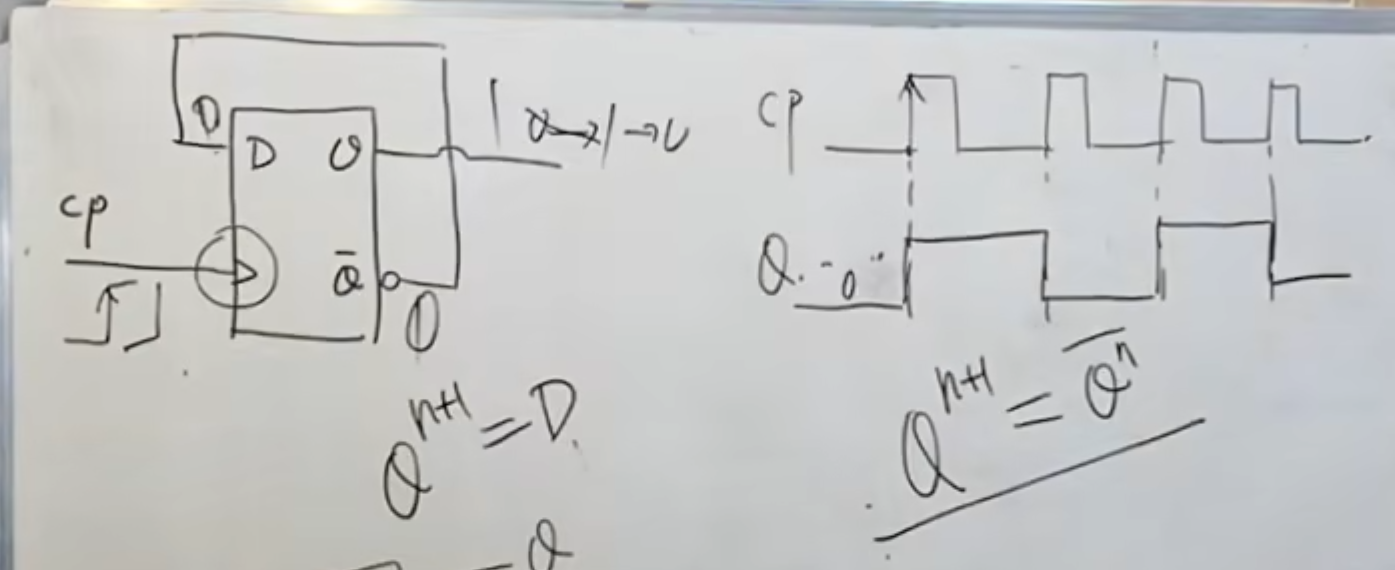

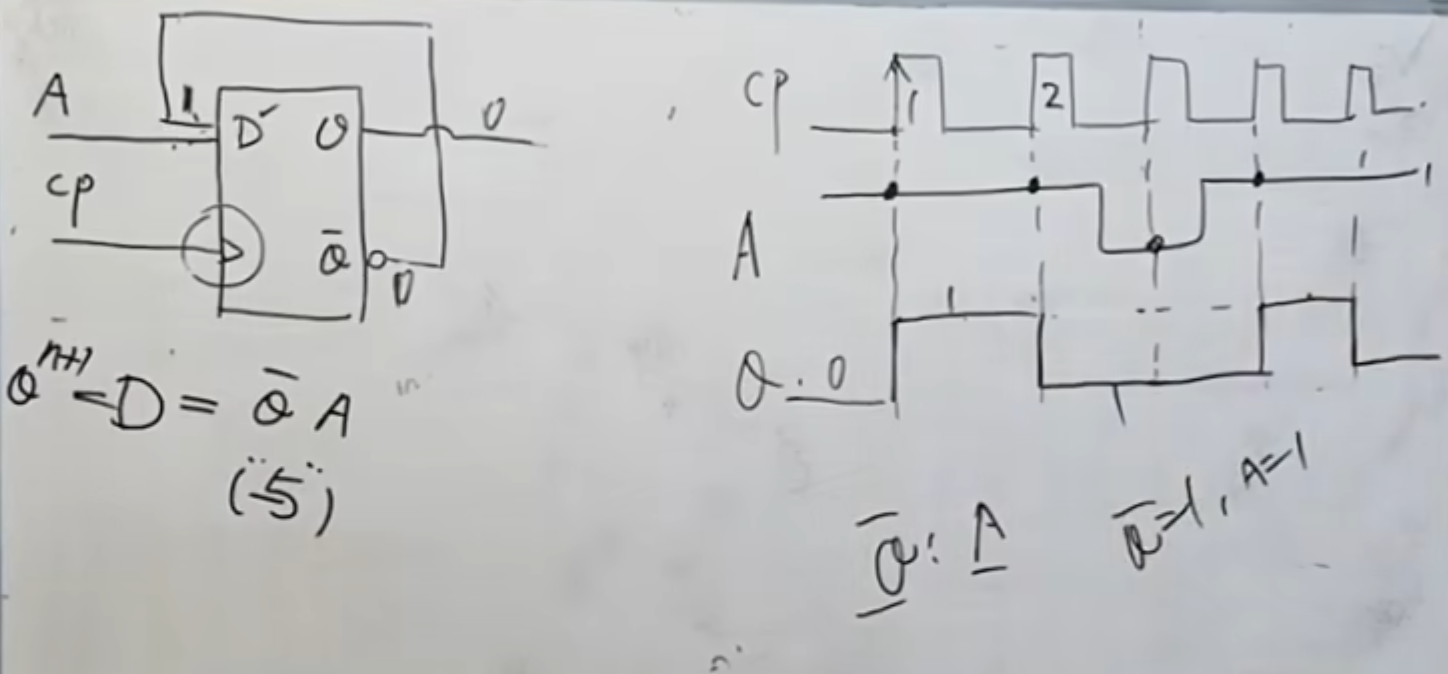

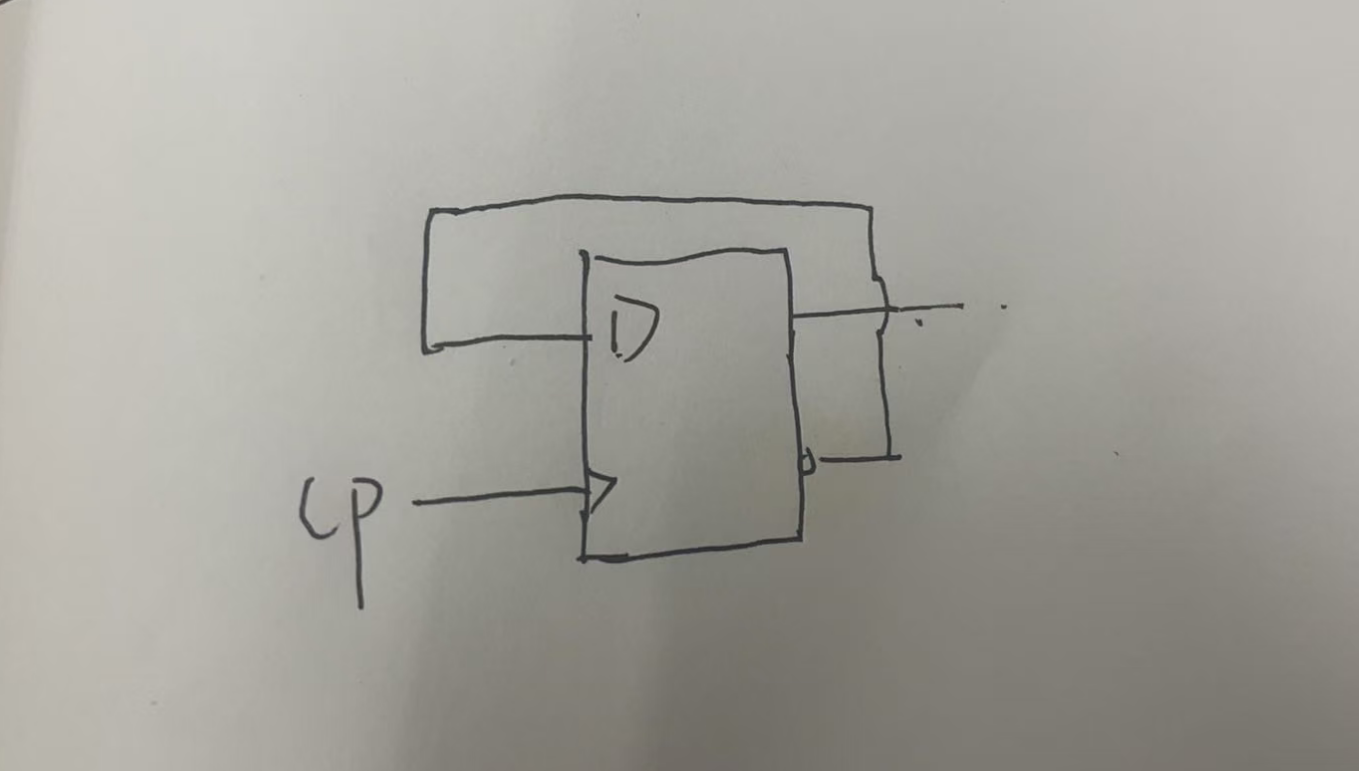

边沿 D 触发器

D 触发器的功能还是比较简单的,首先是看是上升沿触发还是下降沿触发,主要是看输入处有没有圆圈。

其功能表现为与

来一个列题:

NOTE

这里需要注意的是:在

如上面图中的第四个

此外,

那如果

这个时候的输入要看

NOTE

如果没有特别说明,那么这类一个端口上有两个甚至多个输入的情况,认为是相与

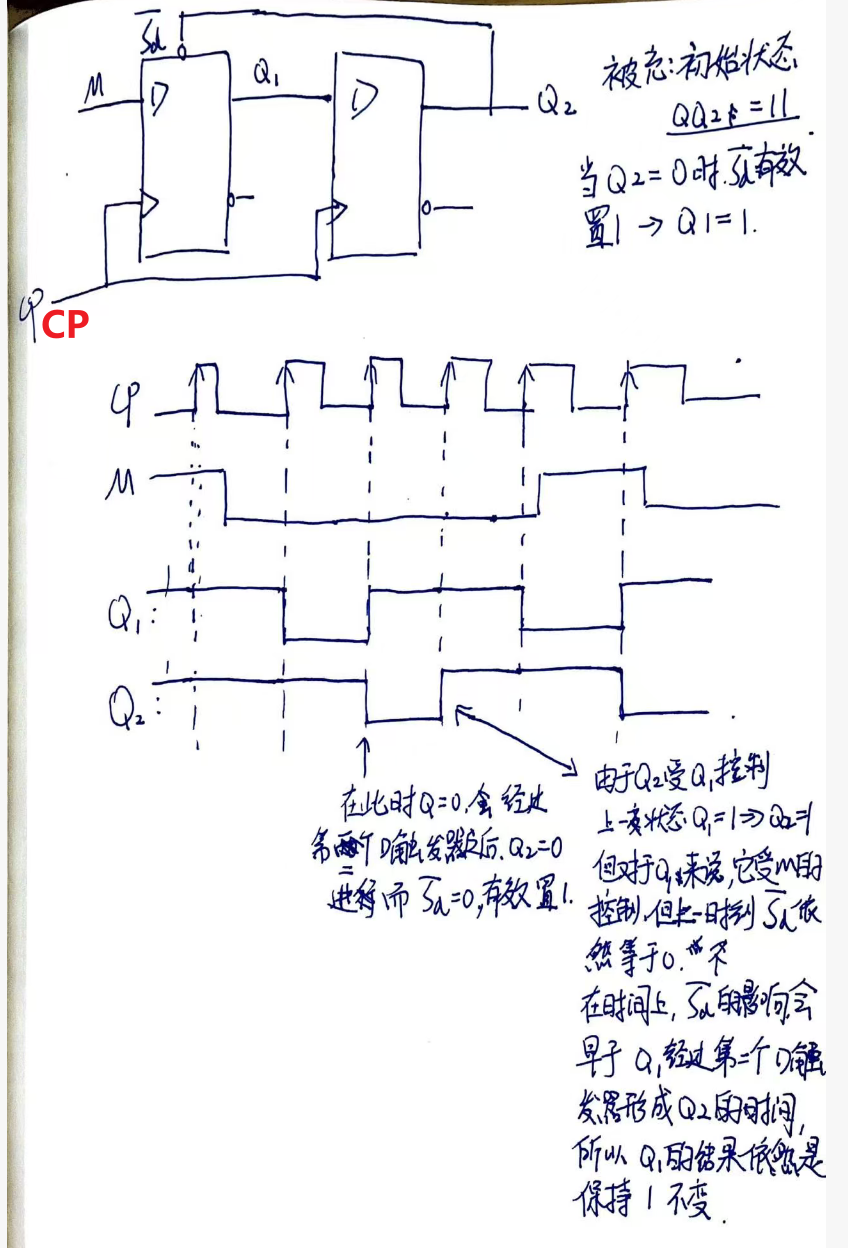

两个

下面进行解释:

这里的核心问题是

对于第一个触发器来说,由于脉冲来的时间是一样的,所以它是直接受到与之相连几个端口的影响的,而它的输出将会再经过一个触发器才会反过来作用到它本身上。这个时候就会出现延时问题

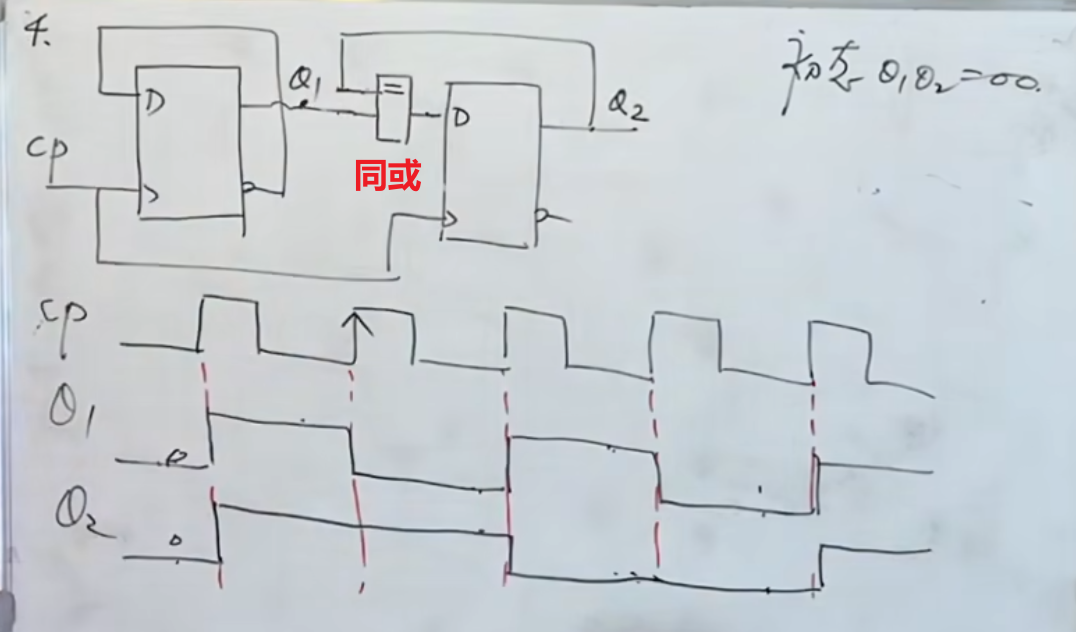

再来一个类似例子:

这个例子是同步

[!tips]

都是上升沿或者下降沿触发就叫做同步,异步则相反:一个上升沿触发,一个下降沿触发。

主要是

T 触发器和 T 撇触发器

其特征方程为:

而

意思就是,只要是来一个脉冲,就发生一次翻转

王海平

王海平